# Educación

Secretaría de Educación Pública

TECNOLÓGICO

NACIONAL DE MÉXICO®

TecNM

Apizaco

TECNOLÓGICO NACIONAL DE MÉXICO

INSTITUTO TECNOLÓGICO DE APIZACO

# INVESTIGACIÓN, DESARROLLO E INNOVACIÓN EN LA INGENIERÍA

(IDII)

Volumen 1, No.1

enero-junio 2025

[www.apizaco.tecnm.mx](http://www.apizaco.tecnm.mx)

**INVESTIGACIÓN, DESARROLLO E INNOVACIÓN EN LA INGENIERÍA

(IDII)**

**Volumen 1, No.1, enero-junio 2025**

**ISSN: En Trámite**

**<https://revista.apizaco.tecnm.mx/ojs/index.php/IDII/index>**

**Tecnológico Nacional de México/Instituto Tecnológico de Apizaco**

**INVESTIGACIÓN, DESARROLLO E INNOVACIÓN EN LA INGENIERÍA**, es un órgano de divulgación científica que se publica de forma semestral editada por el Tecnológico Nacional de México/Instituto Tecnológico de Apizaco. <https://www.apizaco.tecnm.mx/> Av. Instituto Tecnológico No. 418, San Andrés Ahuashuatepec, Municipio de Tzompantepec, Tlaxcala, Méx. C.P. 90491. Correo: [revista@apizaco.tecnm.mx](mailto:revista@apizaco.tecnm.mx)

El contenido y la sintaxis de los artículos presentados son responsabilidad del autor(es). Queda prohibida la reproducción parcial o total del contenido e imágenes de esta publicación en cualquier medio, sin previa autorización por escrito del Tecnológico Nacional de México/Instituto Tecnológico de Apizaco.

# TECNOLÓGICO NACIONAL DE MÉXICO

## INSTITUTO TECNOLÓGICO DE APIZACO

## DIRECTORIO

### **Dr. Ramón Jiménez López**

Director General del Tecnológico Nacional de México

### **Dra. Yesica Imelda Saavedra Benítez**

Directora

### **Mtro. Enrique Acoltzi Bautista**

Subdirector Académico

### **Mtro. Cesar Reynaldo Ramos Gómez**

Subdirector de Planeación y Vinculación

### **Mtro. Abisai Morales Jiménez**

Subdirectora de Servicios Administrativos

### **Dr. Juan Ramos Ramos**

Jefe de la División de Estudios de Posgrado e Investigación

## COMITÉ EDITORIAL

### **Dr. Roberto Morales Caporal**

Editor en Jefe

## COEDITORES

Dr. Raúl Cortés Maldonado

Dra. Raquel Ramírez Amador

Dra. Blanca Estela Pedroza Méndez

Dr. Carlos Bueno Avendaño

Dra. Haydee Patricia Martínez Hernández

## COMITÉ REVISOR

Dr. Jorge Bedolla Hernández

Dr. Rafael Ordoñez Flores

Dra. María Guadalupe Medina Barrera

Dr. Carlos Alberto Mora Santos

Dr. José Federico Ramírez Cruz

Dr. Jorge Luis Castañeda Gutiérrez

Dr. Alan Augusto Gallegos Cuellar

Dr. José Federico Casco Vázquez

Dra. Yesenia Nohemi González Meneses

Dr. Rodolfo Eleazar Pérez Loaiza

Dr. Perfecto Malaquías Quintero Flores

Dr. Antonio Solís Lima

Dr. José Juan Hernández Mora

Dr. Marcos Bedolla Hernández

Dr. José Crispín Hernández Hernández

Dr. Juan Ramos Ramos

Dr. Omar Sandre Hernández

Mtra. María Janai Sánchez Hernández

Mtro. Mario Eduardo Leal López

Mtro. Carlos Pérez Corona

Mtra. Elizabeth Cuatecontzi Cuahutle

Mtro. Eduardo Sánchez Lucero

Pensar para Servir, Servir para Triunfar®

# INDICE

| <b>Artículo</b>                                                                                                                         | <b>pag.</b> |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Diseño e Implementación de Hardware de un PLC con Comunicación Inalámbrica para Aplicaciones de la Industria 4.0                        | 1           |

| Exploración Teórica de Arquitecturas de Microservicios en Entornos Contenerizados                                                       | 11          |

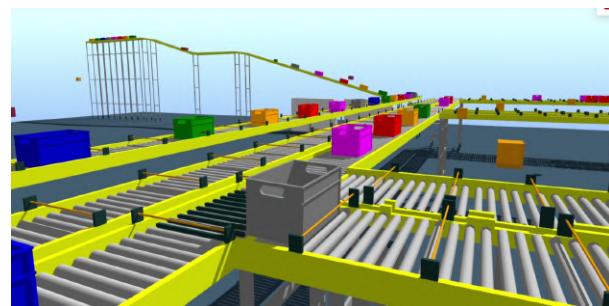

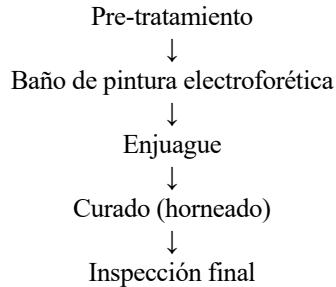

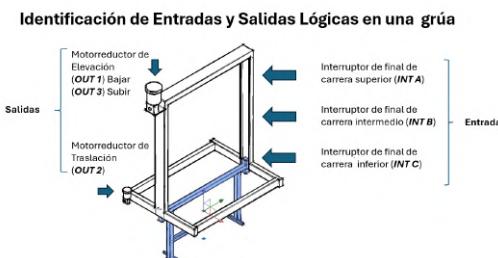

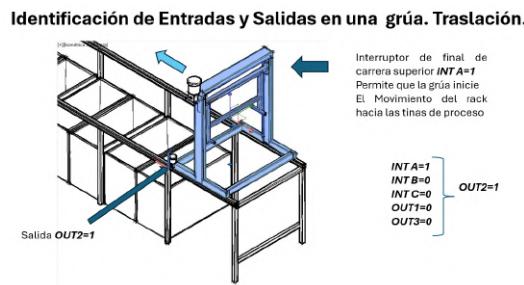

| Construcción del Gemelo Virtual de una Línea de Pintura Electroforética Integrando PLC                                                  | 18          |

| Análisis de Desempeño de Servicios de Notificación en la Nube: Twilio y Google SMTP                                                     | 28          |

| Control Directo de Par de un Motor Síncrono de Imanes Permanentes Aplicado en Electromovilidad Utilizando Redes Neuronales Artificiales | 34          |

| Desarrollo del Hardware de un Inversor Monofásico Puente Completo Basado en MOSFETs para Aplicaciones Fotovoltaicas                     | 44          |

| Diseño, implementación y evaluación de un prototipo Cansat para monitoreo atmosférico                                                   | 51          |

Fecha de recepción: 05 de junio de 2025, fecha de publicación en línea: octubre de 2025.

# Diseño e Implementación de Hardware de un PLC con Comunicación Inalámbrica para Aplicaciones de la Industria 4.0

**Brayan Daniel Vazquez-Gasca, Roberto Morales-Caporal, Carlos Bueno-Avendaño, Rodolfo Eleazar Pérez-Loaiza, y Roy Maza-González**

Tecnológico Nacional de México – Instituto Tecnológico de Apizaco. San Andrés Ahuashuatepec, Municipio de Tzompantepec, Tlaxcala, C.P. 90491, México.

Autor de correspondencia: Brayan Daniel Vázquez Gasca (correo electrónico: m19370518@apizaco.tecnm.mx).

**Abstract** — This article presents the hardware design and implementation of a wireless Programmable Logic Controller. The device integrates eight galvanically isolated digital inputs, three analog inputs, eight relay outputs, and four N-MOS digital outputs. It features a Real-Time Clock (RTC) and utilizes an ESP32 for integrated Wi-Fi and Bluetooth communication. The design emphasizes robust signal conditioning, comprehensive electrical protection, and adherence to IPC standards, aiming for reliable operation in industrial settings. This work provides an open and documented hardware platform suitable for automation and research applications.

**Keywords:** Hardware Design; Industrial Internet of Things (IIoT); Printed Circuit Board (PCB); Programmable Logic Controller (PLC); Wireless Communication

## I. INTRODUCCIÓN

La Industria 4.0 ha redefinido el enfoque de la automatización industrial, al incorporar tecnologías de comunicación inalámbrica, análisis de datos y conectividad en tiempo real en los procesos productivos [1]. En este nuevo entorno, se requiere que los sistemas de control sean más inteligentes, para poder procesar y actuar sobre los crecientes volúmenes de datos generados, optimizar operaciones de manera autónoma y adaptarse dinámicamente a las condiciones cambiantes del proceso, además de ser flexibles e interoperables. Aunque los Controladores Lógicos Programables (PLC) continúan siendo una plataforma esencial en automatización industrial, enfrentan el desafío de adaptarse a entornos digitalizados y distribuidos, especialmente en lo relacionado con módulos de comunicación, conectividad inalámbrica y escalabilidad [2].

De acuerdo con el estado del arte se evidencia una creciente tendencia hacia la integración de tecnologías del Internet Industrial de las Cosas (IIoT) [3], donde la comunicación inalámbrica se vuelve un elemento esencial para la implementación de sistemas ciberfísicos distribuidos [4]. Sin embargo, hoy en día muchos PLCs comerciales operan bajo arquitecturas cerradas y esquemas con licencia, lo que restringe el acceso a su estructura interna y limita su personalización para aplicaciones específicas [5].

El interés por dispositivos de control con conectividad inalámbrica ha crecido en paralelo con la adopción de protocolos como Wi-Fi, Bluetooth, Zigbee y LoRa, los cuales permiten la interacción remota, el monitoreo distribuido y la integración con plataformas de análisis industrial. Esta evolución plantea nuevos desafíos técnicos, incluyendo inmunidad electromagnética, confiabilidad operativa en ambientes adversos, y seguridad en la transmisión de datos [6], [7].

Aunque existen desarrollos recientes orientados a integrar comunicación inalámbrica en sistemas de control, muchos de ellos presentan altos costos, aplicaciones muy específicas o dependen de hardware cerrado [8]. Estas características limitan su adopción en contextos educativos, de investigación o de bajo presupuesto, donde se requiere flexibilidad, documentación abierta y accesibilidad [9].

Este trabajo presenta el diseño e implementación del hardware de un PLC con comunicación inalámbrica integrada, desarrollado bajo el nombre de PLC IIoT ITA-1600. Este dispositivo está orientado a satisfacer requerimientos técnicos y funcionales para la automatización y como plataforma para la investigación en el contexto de la Industria 4.0. El PLC IIoT ITA-1600 se basa en el microcontrolador ESP32, que ofrece conectividad Wi-Fi y Bluetooth, arquitectura de doble núcleo y recursos suficientes para ser usado en aplicaciones industriales [10].

La principal contribución de este trabajo radica en mostrar el proceso de desarrollo de una plataforma de hardware abierto, documentada y escalable, que combina las funcionalidades esenciales de un PLC tradicional con capacidades modernas de conectividad inalámbrica. Esta solución no solo resuelve las limitaciones de PLCs comerciales, sino que también constituye una herramienta didáctica y experimental para el aprendizaje de diseño electrónico orientado a la automatización industrial.

#### A. Controlador Lógico Programable (PLC)

Los PLC son dispositivos electrónicos desarrollados para ejecutar tareas de control secuencial y discreto en sistemas industriales automatizados. Surgieron a finales de la década de 1960 como una alternativa flexible a los sistemas de control cableados basados en relevadores, permitiendo la reconfiguración de procesos mediante programación, sin requerir modificaciones físicas del sistema [11].

Un PLC típico está compuesto por una unidad central de procesamiento (CPU), módulos de entrada/salida (E/S), interfaces de comunicación y una fuente de alimentación. La CPU ejecuta un programa de control lógico almacenado en memoria no volátil, que procesa señales provenientes de sensores conectados a las entradas y envía comandos a actuadores a través de las salidas correspondientes [12].

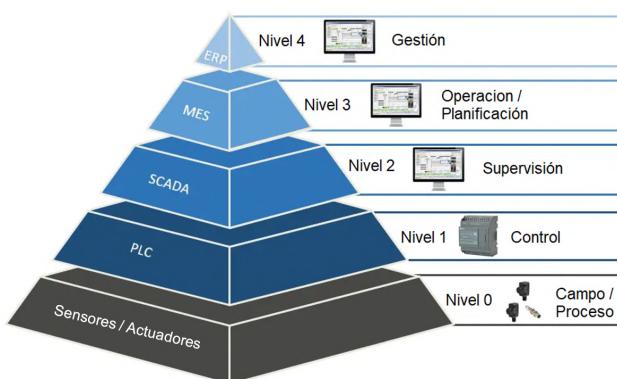

Estos dispositivos se utilizan ampliamente en entornos industriales para la automatización de procesos tanto continuos como discretos, como líneas de ensamble, plantas de tratamiento, sistemas de transporte y control de maquinaria. Dentro de la pirámide de la automatización industrial, los PLC se posicionan como elementos de control local, estableciendo la conexión entre dispositivos de campo (sensores y actuadores) y los niveles superiores de supervisión, como se muestra en la Figura 1 [13].

Figura 1. Pirámide de la automatización industrial [14].

Con la evolución de las arquitecturas de control hacia modelos distribuidos, los PLCs se han integrado en redes industriales mediante protocolos como Modbus, Profibus, EtherCAT o Ethernet/IP, lo que permite su interoperabilidad y coordinación dentro de sistemas jerárquicos de control y monitoreo [15].

#### B. Industria 4.0 e Internet Industrial de las Cosas (IIoT)

La Industria 4.0, también conocida como la cuarta revolución industrial, marca una nueva etapa en la evolución de los sistemas de automatización. Se caracteriza por la integración de tecnologías digitales, de comunicación y procesamiento inteligente de datos en entornos industriales [16]. A diferencia de etapas anteriores, centradas en la mecanización (1.0), la electrificación (2.0) y la automatización eléctrica (3.0), esta fase busca mejorar la eficiencia, flexibilidad y adaptabilidad de los procesos mediante la conectividad entre dispositivos y la toma de decisiones descentralizada [17].

Un componente esencial en la industria 4.0 es el IIoT que aplica los principios del Internet de las Cosas (IoT) al ámbito industrial, donde a través del IIoT, sensores, actuadores, sistemas de control y dispositivos embebidos se conectan mediante redes cableadas o inalámbricas, permitiendo la recolección y análisis de datos en tiempo real [18]. Esta capacidad de monitoreo distribuido y análisis predictivo facilita la optimización de procesos, la detección temprana de fallos y la mejora en la toma de decisiones operativas [19].

El IIoT también permite implementar sistemas conocidos como sistemas ciberfísicos (CPS), en los que el mundo físico y digital interactúan de forma continua [20]. Estas arquitecturas permiten que los sistemas de producción respondan dinámicamente a condiciones cambiantes y se integren con plataformas de análisis en la nube o en el borde de red [21].

En este contexto, dispositivos como los PLCs deben evolucionar hacia arquitecturas más abiertas, escalables y conectadas, que les permitan integrarse como nodos inteligentes dentro de sistemas distribuidos basados en IIoT. Aunque continúan siendo la plataforma dominante en automatización industrial, los PLC enfrentan limitaciones frente a los nuevos requerimientos de conectividad inalámbrica, interoperabilidad y procesamiento distribuido. Estudios recientes destacan que, a pesar de los avances en hardware, el modelo de programación y la estructura de los PLC no han cambiado sustancialmente, lo cual limita su adaptación a entornos más complejos, exigentes y dinámicos como los propuestos por la Industria 4.0 [22].

## II. PLANTEAMIENTO CONCEPTUAL

#### A. Modelo de Desarrollo

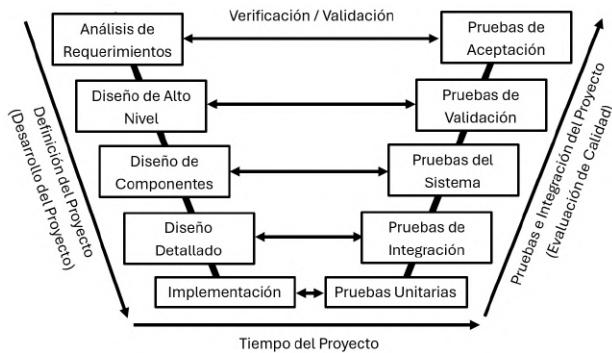

Para estructurar el proceso de diseño e implementación del sistema, se empleó el Modelo V, la cual es una metodología utilizada en el desarrollo de sistemas embebidos [23]. Este enfoque permite establecer una correspondencia directa entre cada etapa de diseño y su fase de verificación, garantizando así su trazabilidad, consistencia y validación durante todo el ciclo de desarrollo del proyecto [24, 25].

La Figura 2 muestra el modelo V aplicado en el desarrollo del presente PLC.

Figura 2: Modelo V para el desarrollo de sistemas embebidos.

El desarrollo del PLC IIoT ITA-1600 siguió las fases de diseño del Modelo V: se inició con el Análisis de Requerimientos (Sección II.A Especificaciones y Requerimientos); seguido por el Diseño de Alto Nivel (Sección II.B Diagrama de Bloques) y el Diseño de Componentes (Sección III. Selección de Componentes); y culminó con el Diseño Detallado y la Implementación del prototipo (Sección IV. Diseño de la Tarjeta PCB).

La validación y verificación se realizó de manera sistemática, asegurando la calidad en cada etapa. En las Pruebas Unitarias, se verificó individualmente cada bloque diseñado (entradas, salidas, RTC, fuente, USB-UART) y su software. Las Pruebas de Integración aseguraron la comunicación y el funcionamiento conjunto entre estos distintos bloques. Posteriormente, en las Pruebas del Sistema, se validó el comportamiento general del PLC como una unidad funcional. Finalmente, las Pruebas de Validación y Aceptación, validadas por el equipo de desarrollo, confirmaron que el dispositivo cumplía con su diseño y los requerimientos iniciales del proyecto (resultados en Sección IV. Resultados), demostrando la funcionalidad del PLC IIoT ITA-1600 para abordar las limitaciones identificadas en PLCs comerciales.

### B. Especificaciones y Requerimientos

A partir de necesidades detectadas en entornos industriales y educativos, se establecieron las siguientes especificaciones y requerimientos del sistema.

-*Interfaces de entrada y salida*: 8 entradas digitales (12–24 VDC) con aislamiento galvánico, 3 entradas analógicas (2 de 0–10 V y 1 de 4–20 mA), 8 salidas a relevador (5 A @ 250 VAC / 30 VDC) y 3 salidas digitales transistorizadas (24 VDC, 100 mA).

-*Comunicación inalámbrica integrada*: Conectividad Wi-Fi (802.11b/g/n) para integración con sistemas IIoT.

-*Capacidades de temporización*: Reloj en tiempo real (RTC) con respaldo de horas para aplicaciones sensibles al tiempo.

-*Interfaces de programación*: Puerto USB para programación y comunicación serial, compatible con entornos de desarrollo estándar.

-*Alimentación*: Entrada de 24 VDC (rango: 22–25 V) con protección contra polaridad inversa. Salida aislada de ±12 VDC para alimentación de sensores externos.

-*Protecciones eléctricas*: Aislamiento galvánico en entradas digitales, protección contra polaridad inversa, filtrado en entradas analógicas y protección contra descargas electrostáticas (ESD).

-*Montaje*: El PLC debe contar con un gabinete de grado industrial con montaje para carril tipo DIN para ser colocado en tableros eléctricos.

-*Condiciones de operación*: Rango de temperatura operativa de -20 °C a 55 °C,

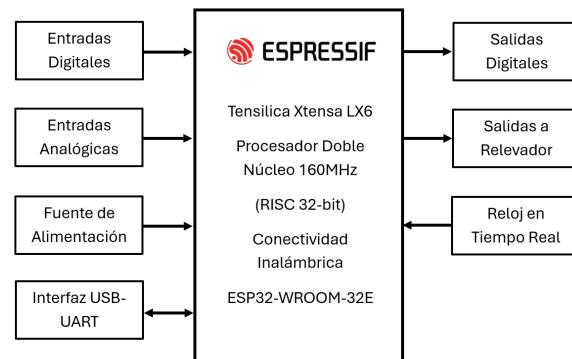

### C. Diagrama de Bloques

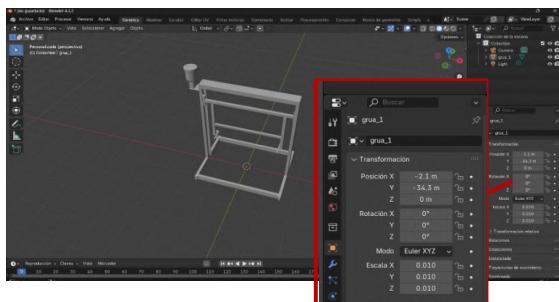

La arquitectura del PLC IIoT ITA-1600 se diseñó conforme a los requerimientos funcionales y especificaciones técnicas definidos. La Figura 3 muestra el diagrama de bloques de alto nivel del sistema, el cual representa los módulos principales de entrada, procesamiento, comunicación y salida.

Figura 3. Diagrama de bloques de alto nivel del PLC IIoT ITA-1600.

El núcleo del sistema está conformado por el microcontrolador ESP32-WROOM-32E-H4, con procesador Xtensa LX6 de doble núcleo a 160 MHz, memoria integrada y conectividad inalámbrica Wi-Fi/Bluetooth. Gracias a su rango de operación de -40 °C a 105 °C, resulta apto para entornos industriales.

Los módulos funcionales que integran el sistema son los siguientes:

-*Entradas digitales (12–24 VDC)*: Incorporan aislamiento galvánico mediante optoacopladores, conformación de señal mediante compuertas Schmitt Trigger y expansión de entradas a través del bus I<sup>2</sup>C.

-*Entradas analógicas (0–10 V y 4–20 mA)*: Incluyen protección contra sobretensiones, filtros pasa-bajas y buffers para adecuar la señal al rango operativo del ADC interno del ESP32.

-*Salidas digitales*: Implementadas mediante transistores N-MOS con capacidad de conmutación de 24 VDC a 100 mA por canal.

**-Salidas a relevador:** Capaces de conmutar cargas de hasta 5 A a 250 VAC o 30 VDC, controladas a través de transistores Darlington.

**-Fuente de alimentación:** A partir de una entrada de 24 VDC, se obtienen líneas internas de 3.3 V y  $\pm 12$  V mediante convertidores DC-DC y reguladores LDO, garantizando aislamiento y estabilidad.

**-Interfaz USB-UART:** Incorpora protección ESD, indicadores de comunicación y circuito de auto-programación para facilitar el desarrollo y la depuración de firmware.

**-Reloj en Tiempo Real (RTC):** Proporciona temporización interna independiente mediante cristal de cuarzo y mantiene la temporización del sistema incluso ante cortes de energía.

### III. SELECCIÓN DE COMPONENTES

Esta sección describe el diseño de los módulos que conforman el PLC IIoT ITA-1600. Para cada bloque funcional, se presenta un resumen de su propósito, las consideraciones técnicas clave y un diagrama esquemático simplificado. En estos diagramas, si un bloque tiene múltiples elementos (como 8 entradas), solo se muestra uno, ya que los mismos criterios aplican para el resto.

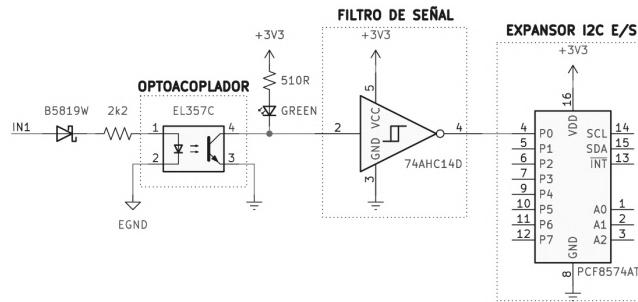

#### A. Entradas Digitales

Este bloque permite la adquisición de señales discretas de 12 a 24 VDC, típicas de sensores industriales, pulsadores o interruptores. El diseño asegura aislamiento galvánico, compatibilidad lógica con el ESP32 y retroalimentación visual del estado de cada canal.

Como se muestra en la Figura 4, se emplea un diodo Schottky B5819 para proteger contra polaridad inversa, gracias a su baja caída de tensión directa y rápida conmutación [26]. Para el aislamiento se seleccionó el optoacoplador EL357, que ofrece una tensión dieléctrica de hasta 3.75 kVrms [27]. La conformación lógica se realiza mediante compuertas Schmitt Trigger 74HC14D, que mejoran la inmunidad al ruido en señales conmutadas [28]. La expansión del número de entradas se logró con el uso del CI PCF8574 que opera mediante el bus I<sup>2</sup>C, permitiendo reducir el número de pines del microcontrolador principal [29].

Figura 4. Diagrama esquemático simplificado de entradas digitales.

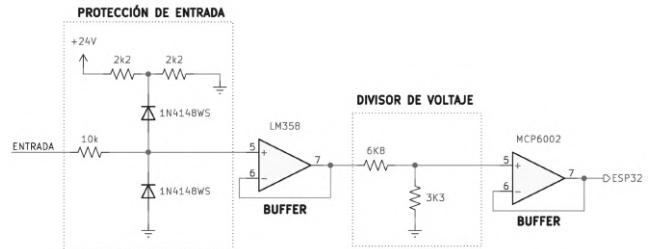

#### B. Entradas Analógicas 0-10 VDC

Este bloque permite la adquisición de señales analógicas de hasta 10 VDC provenientes de transmisores industriales. Se prioriza la protección contra condiciones anómalas, la

adaptación del nivel de voltaje y la preservación de la impedancia para el ADC del ESP32.

Figura 5. Diagrama esquemático de entradas analógicas de 0-10 V.

Como se observa en la Figura 5, se implementa una etapa de protección contra sobretensión ( $+12$  VDC) y polaridad inversa, basada en diodos de señal y resistores configurados en modo clamp diode [30]. La señal protegida se acopla a un amplificador operacional LM358 en configuración seguidor de voltaje, seleccionado por su capacidad de operar con 24 VDC y proporcionar alta impedancia de entrada [31].

La adaptación de nivel se realiza mediante un divisor resistivo que reduce la señal de entrada de 0-10 V a un rango seguro para el ADC del ESP32 (0-3.3 V). En este diseño, la salida del divisor ( $V_{ADC}$ ) alcanza un valor de 3.2673 V cuando se aplican 10 V en la entrada, lo cual se considera dentro del margen aceptable para el ADC, aunque debe ajustarse en el firmware. El cálculo se muestra en la ecuación (1):

$$V_{ADC} = \frac{3300 \Omega}{6800 \Omega + 3300 \Omega} \cdot 10 V = 3.2673 V \quad (1)$$

Para garantizar la estabilidad de este voltaje y evitar variaciones ante cambios de carga, se añade un segundo buffer utilizando el amplificador operacional MCP6002, que proporciona operación riel a riel en entradas y salidas [32].

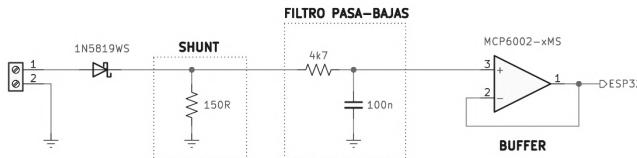

#### C. Entrada Analógica 4-20 mA DC

Este bloque permite leer señales de corriente de lazo de 4 a 20 mA, ampliamente utilizadas en instrumentación industrial por su inmunidad al ruido y robustez [33]. Como se observa en la Figura 6 la corriente fluye a través de un diodo Schottky que protege contra polaridad inversa, y posteriormente pasa por un resistor de derivación (shunt) de 150  $\Omega$  que genera una caída de voltaje de 0.6 a 3 V, el cálculo se muestra en la ecuación (2) y ecuación (3).

$$V_{SHUNT_{min}} = (150 \Omega)(4 \times 10^{-3} A) = 0.6 V \quad (2)$$

$$V_{SHUNT_{max}} = (150 \Omega)(20 \times 10^{-3} A) = 3 V \quad (3)$$

La señal se filtra mediante un RC pasa-bajas y se estabiliza con un buffer basado en el MCP6002, manteniendo la integridad antes del muestreo del ADC, de igual forma se debe

acondicionar los valores mínimos y máximos mediante firmware.

Figura 6. Diagrama esquemático de entrada analógica de 4-20

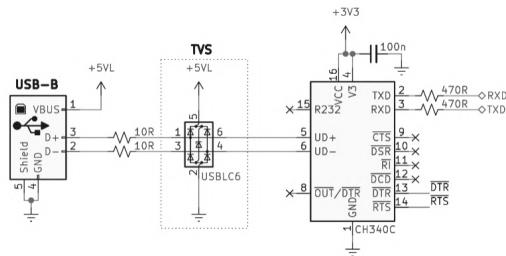

#### D. Interfaz USB-UART

El bloque USB-UART permite la programación y depuración directa del PLC mediante un conector USB tipo B. La Figura 7a muestra el circuito de conversión de USB a UART para la comunicación y programación del ESP32. La figura 7b muestra el circuito para la programación automática y botones para su programación manual, siguiendo recomendaciones del fabricante [34]

Figura 7a. Diagrama esquemático de conversor USB-UART.

Figura 7b. Diagrama esquemático de auto-programación y botones de programación manual.

Se emplea el conversor CH340C por su fiabilidad, facilidad de integración y compatibilidad con USB 2.0. Las líneas D+ y D- incluyen resistores de impedancia de 10Ω y protección ESD mediante el circuito TVS USBLC6-2SC6 [35]. LEDs indicadores permiten visualizar la transmisión (TXD) y recepción (RXD) de datos.

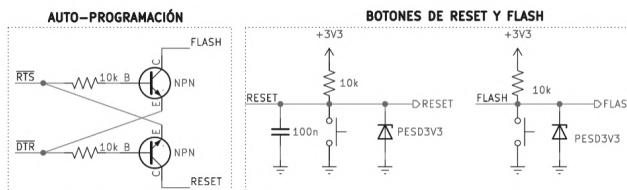

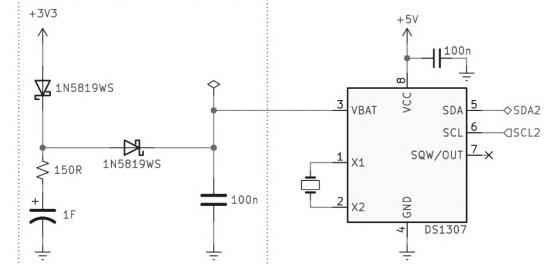

#### E. Reloj en Tiempo Real (RTC)

El sistema incorpora un reloj DS1307 con comunicación I<sup>2</sup>C, capaz de mantener la hora y fecha durante cortes de energía [36], seleccionado debido a su uso adecuado para aplicaciones de temporización como, invernaderos para programar horarios de riego. La Figura 8 muestra el diagrama esquemático del bloque.

El respaldo de energía del RTC se implementa mediante un supercapacitor de 1F / 5.5V, seleccionado por su

compactidad, larga vida útil y eliminación de mantenimiento en comparación con baterías de litio [37].

Este se carga durante la operación normal del PLC y mantiene activo el reloj cuando la fuente principal de alimentación se interrumpe.

#### RESPALDO DE HORA Y FECHA

Figura 8. Diagrama esquemático de Reloj en Tiempo Real.

Para limitar la tensión de carga a 3 V, se emplea un diodo Schottky 1N5819WS, cuya baja caída de voltaje directa resulta adecuada para esta aplicación, con  $V_D = 0.3 V$ . Dado que un supercapacitor descargado se comporta inicialmente como un cortocircuito [38], se incorpora un resistor en serie para limitar la corriente de irrupción durante la conexión inicial cuando se conecta el PLC a la energía. El valor se seleccionó para restringir la corriente a un máximo de 20 mA, como se muestra en la ecuación (4).

$$R_C = \frac{V_s - V_D}{I} = \frac{3.3 V - 0.3 V}{20 \times 10^{-3} A} = 150 \Omega \quad (4)$$

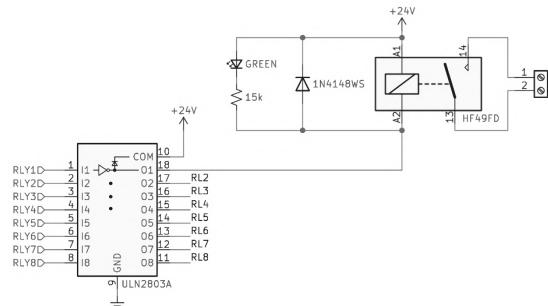

#### F. Salidas a Relevador

Este bloque permite el control de cargas mediante relevadores SPST de 24 V activados por lógica del PLC, la Figura 9 muestra el diagrama simplificado.

Figura 9. Diagrama esquemático simplificado de salidas a relevador.

Cada canal es operado por el circuito integrado Darlington ULN2803, seleccionado debido a que soporta hasta 500 mA por salida y cuenta con diodos flyback internos [39]. Se incluye un diodo externo 1N4148WS por canal para redundancia. El relevador utilizado HF49FD permite conmutar hasta 5 A en 250 VAC o 30 VDC lo que es ideal para manejar pequeñas cargas o contactores para más capacidad de corriente [40].

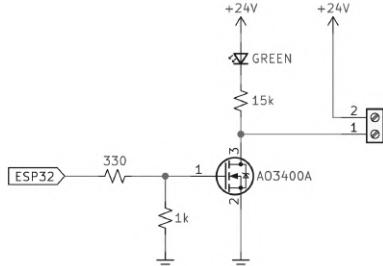

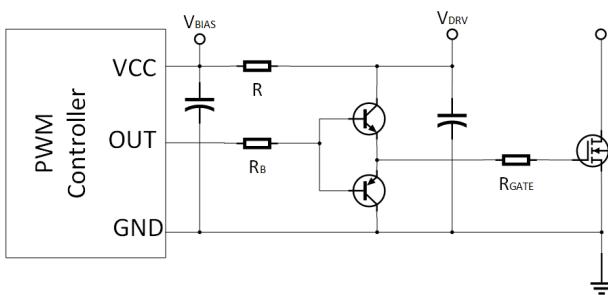

### G. Salidas a Transistor

Este bloque permite la conmutación directa de cargas en corriente continua, tales como semáforos o actuadores industriales, mediante transistores tipo N-MOSFET. La Figura 10 presenta el esquema simplificado del circuito.

Figura 10. Diagrama simplificado de salidas a transistor.

Cada canal es controlado por un transistor AO3400, seleccionado por su baja resistencia de encendido  $\approx 30\text{ m}\Omega$  [41]. La compuerta de cada MOSFET incorpora un resistor limitador de  $330\text{ }\Omega$ , que protege el pin GPIO del microcontrolador ante picos de corriente producidos por la carga capacitiva de la compuerta durante la conmutación. Además, se utiliza un resistor pull-down de  $1\text{ k}\Omega$  para garantizar que el transistor permanezca apagado durante el arranque del sistema, evitando activaciones indeseadas [42].

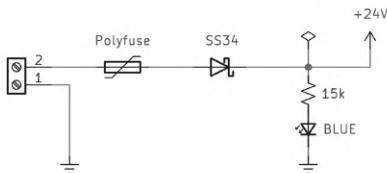

### H. Fuente de Alimentación

El sistema de alimentación se compone de varias etapas reguladoras que derivan y distribuyen las tensiones necesarias a partir de una entrada única de 24 VDC.

Figura 11. Diagrama esquemático de protección de entrada.

La Figura 11 muestra el bloque inicial, diseñado para proteger al sistema frente a condiciones eléctricas adversas. Este bloque incluye un fusible PPTC (1.85 A, 30 V), dimensionado según la corriente máxima estimada del sistema ( $\approx 1.5\text{ A}$ ), con capacidad de recuperación automática tras una sobrecorriente moderada. Para proteger contra polaridad inversa, se emplea un diodo Schottky SS34, capaz de manejar hasta 3 A con baja caída de voltaje directo [43].

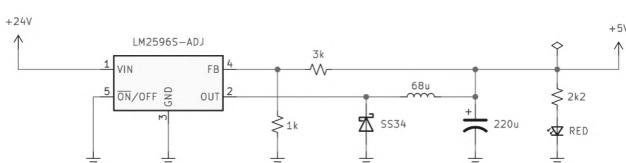

La conversión primaria se realiza mediante el regulador conmutado XL2596S-5.0E1, representado en la Figura 12.

Figura 12. Diagrama esquemático de regulación primaria de 5 V.

Este regulador fue seleccionado por su alta eficiencia ( $>70\%$ ), capacidad de corriente de hasta 3 A y su operación estable hasta 40 V de entrada. El diseño incluye un inductor blindado de  $68\text{ }\mu\text{H}$ , un diodo Schottky SS34 y un capacitor electrolítico de  $220\text{ }\mu\text{F}$ , dichos componentes son sugeridos por el fabricante para garantizar estabilidad y baja ondulación en la salida [44]. Un LED rojo indica la presencia de 5 V.

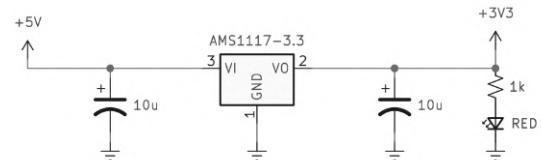

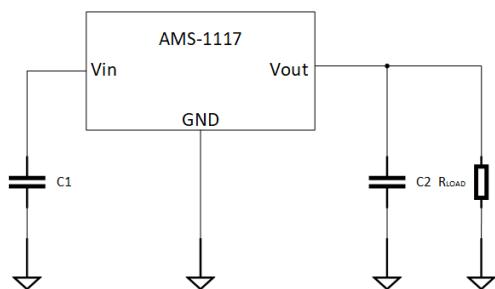

Para alimentar la lógica de bajo voltaje (ESP32 y periféricos), se emplea un regulador lineal de baja caída (LDO) AMS1117-3.3, mostrado en la Figura 13.

Figura 13. Diagrama esquemático de regulación de 3.3 V.

Este componente fue elegido por su bajo ruido de salida, capacidad de corriente de hasta 1 A. A la entrada y salida se integran capacitores de tantalio de  $10\text{ }\mu\text{F}$  de baja ESR, recomendados por el fabricante para garantizar estabilidad en aplicaciones sensibles a interferencias [45].

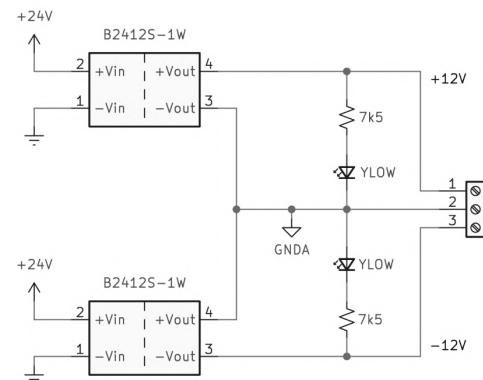

Figura 14. Diagrama esquemático de salida simétrica de  $\pm 12\text{ V}$ .

La Figura 14 ilustra el bloque encargado de generar una salida aislada de voltaje simétrico que permite alimentar sensores o módulos analógicos que requieran alimentación simétrica. Este bloque utiliza dos convertidores DC-DC B2412S-1W, conectados en serie y configurados para entregar salidas de  $\pm 12\text{ V}$  referidas a una tierra flotante, cada convertidor puede entregar hasta 84 mA de corriente continua con aislamiento galvánico de 1 kV [46].

## IV. DISEÑO DE LA TARJETA PCB

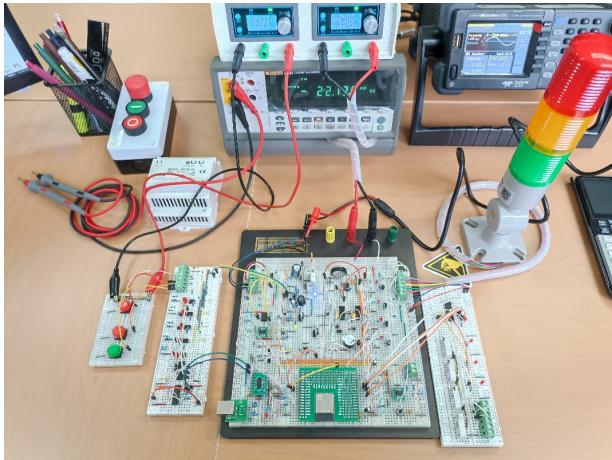

### A. Prototipo de Validación Funcional

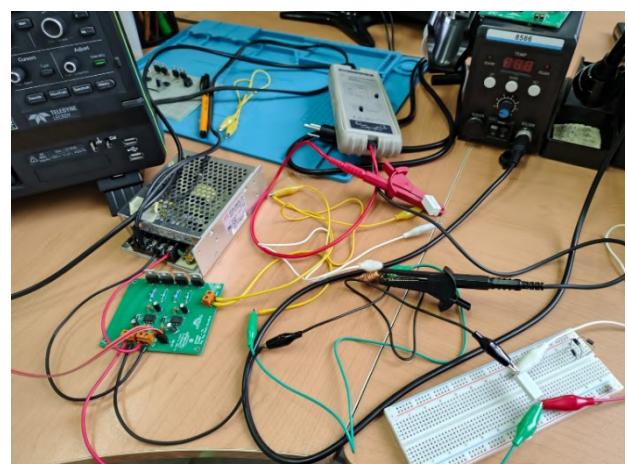

Una vez realizada la selección de componentes del PLC, se procedió a la implementación del prototipo. El circuito se ensambló en protoboard dentro del laboratorio, donde se efectuaron pruebas unitarias y de integración para validar el correcto funcionamiento de cada bloque diseñado. En esta

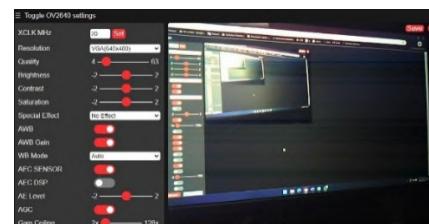

etapa, se realizaron mediciones directas de niveles de tensión, se evaluaron los tiempos de respuesta en las entradas y salidas, y se verificó la comunicación entre los distintos módulos funcionales (microcontrolador con expansores I<sup>2</sup>C, RTC), dichas pruebas fueron realizadas dentro del laboratorio de prueba con equipos de medición y prueba profesionales. Estos ensayos preliminares confirmaron la operación individual de cada componente y la correcta interacción entre los bloques, asegurando la viabilidad del diseño antes de proceder a la fabricación de la tarjeta final. La Figura 15 presenta el prototipo utilizado para estas validaciones funcionales.

Figura 15. Ensamble funcional del prototipo en protoboards durante

las pruebas validación del diseño.

### B. Diseño de PCB

El diseño se realizó conforme a estándares internacionales que garantizan la confiabilidad, seguridad y calidad del producto final. Se consideraron las siguientes normativas:

-*IPC-2221B* [47]: Norma general para el diseño de placas de circuito impreso, establece los requisitos mínimos para el espaciado entre conductores, dimensiones de pistas y vías, selección del espesor del cobre, aislamiento, y consideraciones térmicas. Proporciona los lineamientos base para asegurar manufacturabilidad, seguridad eléctrica y durabilidad del diseño.

-*IPC-A-610* [48]: Estándar de aceptabilidad para ensambles electrónicos. Define los criterios de inspección visual y calidad para las soldaduras, montaje de componentes y acabados. Es ampliamente utilizado para certificar la calidad de ensamblajes en la industria electrónica.

#### • Consideraciones Técnicas

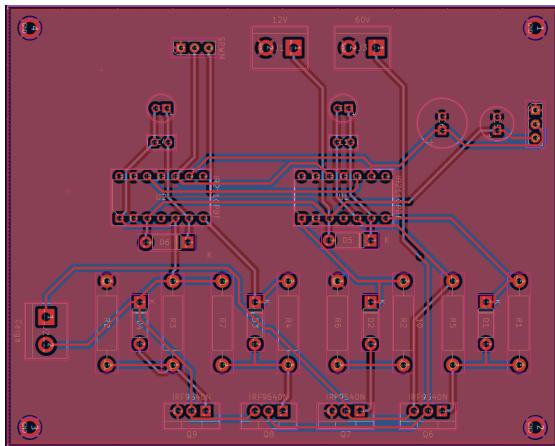

El acomodo de los componentes se realizó tomando en cuenta las dimensiones del gabinete, empleando una PCB de 122.6 mm × 87.7 mm. La distribución se organizó por bloques funcionales (entradas, salidas, fuente de alimentación y procesamiento), priorizando la separación física y la reducción de interferencia electromagnética (EMI). El diseño siguió las

recomendaciones de la norma IPC-2221, manteniendo una separación clara entre las zonas de potencia y las de señal, con el fin de evitar acoplamientos parásitos.

Se aplicaron planos de tierra en ambas capas para mejorar la integridad de señal y el ruido EMI. Las pistas de potencia, diseñadas para soportar hasta 5 A (relevadores), se dimensionaron con un ancho de 2.7 mm, distribuidas en ambas caras, conforme a cálculos basados en IPC-2221 para asegurar una adecuada disipación térmica.

Las señales de bajo nivel se trazaron con pistas más delgadas, con separación suficiente para evitar diafonía. En las zonas críticas, como los optoacopladores y relevadores, se implementaron ranuras de aislamiento de 2 mm, incrementando la distancia de fuga para prevenir arcos eléctricos [49].

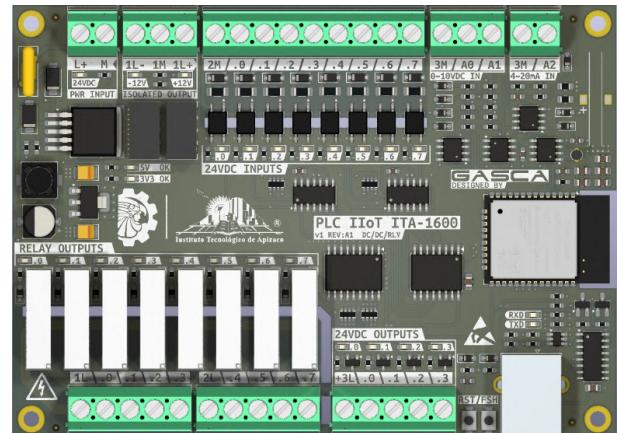

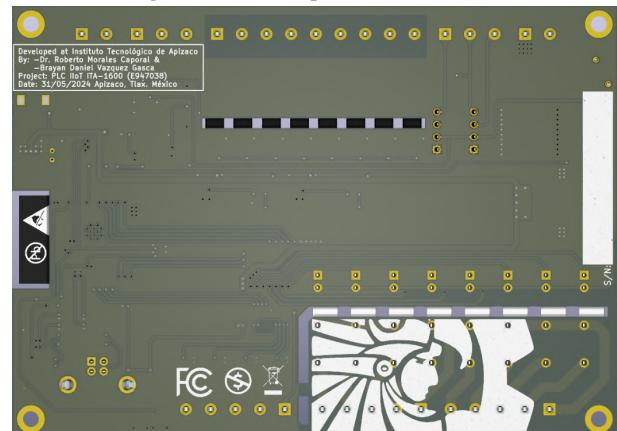

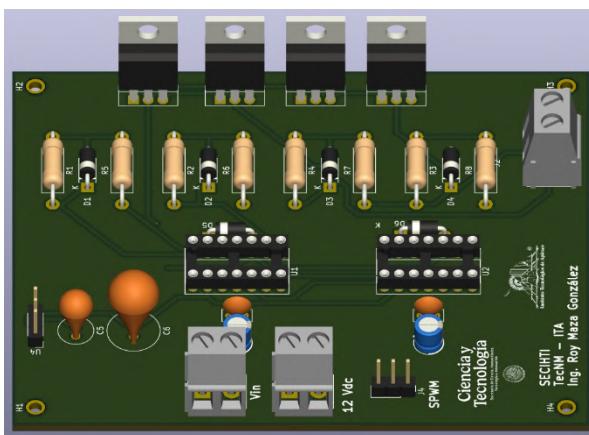

El uso de herramientas CAD especializadas fue esencial en este proceso, permitiendo el diseño esquemático, la disposición de componentes, el trazado de pistas y la ejecución de verificaciones automáticas de reglas de diseño (DRC). Estas herramientas también permiten generar una visualización tridimensional (3D) del diseño, como se muestra en las Figuras 16 y 17, facilitando la validación de la integración mecánica, el posicionamiento correcto de los componentes y la compatibilidad dimensional con el gabinete. Esta verificación visual es crucial antes de proceder a la generación de archivos de fabricación

Figura 16. Vista superior de modelo 3D

Figura 17. Vista inferior de modelo 3D.

### C. Fabricación y Ensamble

Una vez finalizado el diseño de la PCB y verificado mediante simulación y visualización tridimensional, se procedió a la generación de los archivos de fabricación Gerber, estos archivos fueron elaborados de acuerdo con las especificaciones previamente establecidas en las reglas de diseño, garantizando compatibilidad con procesos industriales de fabricación en doble capa, calidad Clase 2, y materiales dieléctricos FR4 con acabado superficial estándar.

Tras la recepción de las placas de circuito impreso (PCBs), se llevó a cabo una inspección visual inicial bajo los lineamientos establecidos por la norma IPC-A-600, con el objetivo de verificar la calidad de manufactura, el estado de los pads, la alineación de las serigrafías, y la integridad del cobre y de las vías.

Posteriormente, se procedió al ensamblaje manual de los componentes eléctricos y electrónicos sobre las PCBs, soldando así un total de 198. Para asegurar la correcta colocación de cada componente se utilizó una lista de materiales (BOM) interactiva con vista esquemática, que permite identificar de manera precisa la ubicación de cada referencia. Esto fue útil, debido a que, para optimizar espacio no se imprimieron referencias tipo "R1", "U1", etc., en la serigrafía, manteniendo únicamente las marcas de polaridad y orientación de cada componente.

Una vez finalizado el montaje, se efectuó una inspección visual completa de la tarjeta de circuito impreso ensamblada (PCBA) utilizando microscopio digital, conforme a los criterios de aceptabilidad establecidos por la norma IPC-A-610 para productos Clase 2. Se evaluaron aspectos como la forma de las soldaduras, la presencia de puentes, la alineación de terminales y la limpieza del sustrato.

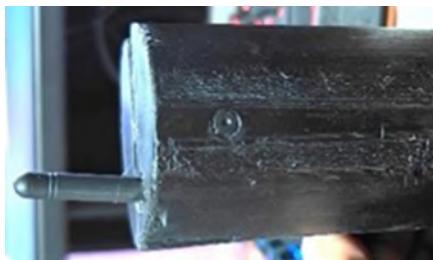

## V. RESULTADOS

Una vez completado el proceso de diseño, fabricación y ensamblaje del PLC IIoT ITA-1600, se presenta el dispositivo final completamente ensamblado y montado en su gabinete, destacando su estructura física, distribución y características técnicas principales.

Figura 18. Vista del PLC IIoT ITA-1600 completamente ensamblado.

La Figura 18 muestra el aspecto final del controlador, cuyas especificaciones principales se resumen en la Tabla I. La documentación del proyecto se puede encontrar en el repositorio oficial en GitHub [50].

Tabla I. Especificaciones técnicas del PLC IIoT ITA-1600

| Categoría               | Especificación                                                                                                                                  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Indicadores             | Indicadores LED                                                                                                                                 |

| Montaje                 | Sobre perfil DIN de 35 mm                                                                                                                       |

| Alimentación            | 24 VDC nominal (22–25 VDC) <ul style="list-style-type: none"> <li>• Protección de polaridad: Sí</li> </ul>                                      |

| RTC                     | Respaldo de hora: 48 horas (sin energía)                                                                                                        |

| Entradas Digitales      | 8 canales (12–24 VDC) <ul style="list-style-type: none"> <li>• Aislamiento: 3.75 kV</li> <li>• Frecuencia: hasta 1 kHz</li> </ul>               |

| Entradas Analógicas     | 2× (0–10 V, > 1 MΩ) • 1× (4–20 mA, 150 Ω) <ul style="list-style-type: none"> <li>• Protección: hasta 24 V</li> <li>• Sin aislamiento</li> </ul> |

| Salidas a Relevador     | 8 canales (4×2 grupos) <ul style="list-style-type: none"> <li>• 250 VAC/30 VDC, 5 A máx.</li> <li>• Vida útil: 50,000 ciclos</li> </ul>         |

| Salidas Digitales       | 4 canales tipo N-MOS <ul style="list-style-type: none"> <li>• 24 VDC, 100 mA máx.</li> <li>• Sin protección contra cortos</li> </ul>            |

| Conectividad            | • Wi-Fi 802.11b/g/n (150 Mbps máx.)<br>• Bluetooth 4.2 BLE + BR/EDR                                                                             |

| CPU                     | ESP32-D0WD-V3 / ESP32-D0WDR2-V3 <ul style="list-style-type: none"> <li>• 2 núcleos @ 240 MHz</li> <li>• 520 KB SRAM + 2 MB PSRAM</li> </ul>     |

| Condiciones ambientales | • Operación: -20 °C a 55 °C                                                                                                                     |

| Dimensiones             | • Almacenaje: -40 °C a 70 °C<br>145 × 90 × 40 mm (Ancho × Alto × Profundidad)                                                                   |

Para validar el correcto funcionamiento se realizaron pruebas de validación en laboratorio, incluyendo mediciones de niveles de tensión, tiempos de respuesta y la operación de entradas y salidas bajo cargas como motores monofásicos. Estas pruebas, ejecutadas tanto en los protoboard iniciales como en el prototipo final de la PCB, confirmaron la integridad de la señal y la consistencia operativa del PLC IIoT ITA-1600 con su diseño, demostrando su viabilidad funcional en un entorno controlado.

## VI. CONCLUSIONES

Este trabajo presentó el desarrollo del PLC IIoT ITA-1600 orientado a aplicaciones industriales y educativas, que integra entradas y salidas digitales y analógicas, comunicación USB-UART y un reloj en tiempo real. El diseño de hardware se llevó a cabo siguiendo la metodología del modelo en V, abarcando desde la concepción inicial hasta la implementación del dispositivo físico. Desde las primeras etapas, se priorizó la

robustez eléctrica, aplicando buenas prácticas de diseño electrónico, como el uso de planos de tierra, ranuras de aislamiento y dimensionamiento de pistas conforme a las normativas internacionales.

Este dispositivo sienta una base sólida para futuros trabajos de investigación y desarrollo, incluyendo la implementación de protocolos de comunicación IIoT avanzados (como MQTT) para la integración directa con plataformas de análisis en la nube. Las pruebas de validación realizadas en laboratorio confirman su operación, sentando las bases para futuras validaciones de rendimiento en entornos industriales reales, como pruebas de compatibilidad electromagnética (EMI) y resistencia a la vibración, entre otras.

## REFERENCIAS

- [1] M. Noor-A-Rahim, J. John, F. Firyaguna, H. H. R. Sherazi, S. Kushch, A. Vijayan, E. O'Connell, D. Pesch, B. O'Flynn, W. O'Brien, M. Hayes, and E. Armstrong, "Wireless Communications for Smart Manufacturing and Industrial IoT: Existing Technologies, 5G and Beyond," *Sensors*, vol. 23, no. 1, p. 73, 2023, doi: 10.3390/s23010073.

- [2] K.-C. Yao, C.-L. Lin, and C.-H. Pan, "Industrial Sustainable Development: The Development Trend of Programmable Logic Controller Technology," *Sustainability*, vol. 16, no. 14, p. 6230, 2024, doi: 10.3390/su16146230.

- [3] Z. Liu, F. Davoli, and D. Borsatti, "Industrial Internet of Things (IIoT): Trends and Technologies," *Future Internet*, vol. 17, no. 5, p. 213, 2025. doi: 10.3390/fi17050213.

- [4] H. Xu, W. Yu, D. Griffith and N. Golmie, "A Survey on Industrial Internet of Things: A Cyber-Physical Systems Perspective," in *IEEE Access*, vol. 6, pp. 78238-78259, 2018, doi: 10.1109/ACCESS.2018.2884906.

- [5] M. Würcher, "The evolution of PLCs driving Industry 4.0 forward: How robust and secure semiconductor solutions are providing the brains and the brawn in Next-Generation PLCs, enabling smart factories to meet increasing system requirements," Infineon Technologies, Germany, [Online]. Available: <https://tinyurl.com/2vu77daw>. [Accessed: May 12, 2025].

- [6] L. L. Dhirani, E. Armstrong, and T. Newe, "Industrial IoT, Cyber Threats, and Standards Landscape: Evaluation and Roadmap," *Sensors*, vol. 21, no. 11, p. 3901, 2021, doi: 10.3390/s21113901.

- [7] J. Hajda, R. Jakuszewski, and S. Ogonowski, "Security Challenges in Industry 4.0 PLC Systems," *\*Appl. Sci.\**, vol. 11, no. 21, p. 9785, 2021, doi: 10.3390/app11219785.

- [8] L. I. Minchala, J. Peralta, P. Mata-Quevedo, and J. Rojas, "An Approach to Industrial Automation Based on Low-Cost Embedded Platforms and Open Software," *Appl. Sci.*, vol. 10, no. 14, p. 4696, 2020. doi: 10.3390/app10144696

- [9] A. Soriano, L. Marín, M. Vallés, A. Valera, and P. Albertos, "Low Cost Platform for Automatic Control Education Based on Open Hardware," *IFAC Proc. Volumes*, vol. 47, no. 3, pp. 9044-9050, 2014.

- [10] Espressif Systems, "ESP32" 2024. [Online]. Available: <https://www.espressif.com/en/products/socs/esp32>. [Accessed: May 13, 2025]

- [11] M. A. Sehr et al., "Programmable Logic Controllers in the Context of Industry 4.0," in *IEEE Transactions on Industrial Informatics*, vol. 17, no. 5, pp. 3523-3533, May 2021, doi: 10.1109/TII.2020.3007764.

- [12] K.-C. Yao, C.-L. Lin, and C.-H. Pan, "Industrial Sustainable Development: The Development Trend of Programmable Logic Controller Technology," *Sustainability*, vol. 16, no. 14, Art. no. 6230, Jul. 2024. doi: 10.3390/su16146230.

- [13] F. J. Folgado, D. Calderón, I. González, and A. J. Calderón, "Review of Industry 4.0 from the Perspective of Automation and Supervision Systems: Definitions, Architectures and Recent Trends," *Electronics*, vol. 13, no. 4, Art. no. 782, Feb. 2024. doi: 10.3390/electronics13040782.

- [14] Z. Parham, "Enabling Sustainability through all Levels of the Automation Pyramid," *Software Toolbox Blog*, 25 Abr. 2024. [En línea]. Disponible en: <https://blog.softwaretoolbox.com/earth-day-automation-pyramid>

- [15] B. Joshi, "A Study of the Various Communication Protocols Used in PLC Systems: Modbus, Profibus, Ethernet/IP and Their Implementations, Evolution and Comparative Analysis," *International Research Journal of Modernization in Engineering Technology and Science*, vol. 6, no. 4, pp. 3535-3542, Apr. 2024, doi: 10.56726/IRJM

- [16] E. Oztemel and S. Gursev, "Literature review of Industry 4.0 and related technologies," *Journal of Intelligent Manufacturing*, vol. 31, no. 1, pp. 127-182, Jan. 2020, doi: 10.1007/s10845-018-1433-8.

- [17] S. S. Singh, "Industry 4.0: A Comprehensive Review and Future Perspectives," *International Journal for Research in Applied Science & Engineering Technology (IJRASET)*, vol. 11, no. VII, pp. 1945-1947, Jul. 2023.

- [18] S. Munirathinam, "Industry 4.0: Industrial Internet of Things (IIoT)," *Advances in Computers*, vol. 117, Academic Press, 2020, pp. 129-164. doi: 10.1016/bs.adcom.2019.10.010

- [19] M. Soori, B. Arezoo, and R. Dastres, "Internet of things for smart factories in industry 4.0, a review," *Internet of Things and Cyber-Physical Systems*, vol. 3, pp. 192-204, 2023. doi: 10.1016/j.iotcps.2023.04.006.

- [20] P. O'Donovan, C. Programmable Logic Controllers in the Context of Industry 4.0, K. Bruton, and D. T. J. O'Sullivan, "A fog computing industrial cyber-physical system for embedded low-latency machine learning Industry 4.0 applications," *Manufacturing Letters*, vol. 15, Part B, pp. 139-142, Jan. 2018, doi: 10.1016/j.mfglet.2018.01.005.

- [21] C. Yang, S. Lan, W. Shen, L. Wang and G. Q. Huang, "Software-defined Cloud Manufacturing with Edge Computing for Industry 4.0," *2020 International Wireless Communications and Mobile Computing (IWCMC)*, Limassol, Cyprus, 2020, pp. 1618-1623, doi: 10.1109/IWCMC48107.2020.9148467.

- [22] J.-Y. Chen, K.-C. Tai, and G.-C. Chen, "Application of Programmable Logic Controller to Build-up an Intelligent Industry 4.0 Platform," *Procedia CIRP*, vol. 63, pp. 150-155, 2017, doi: 10.1016/j.procir.2017.03.116.

- [23] R. Morales-Caporal, A. S. Reyes-Galaviz, J. F. Casco Vasquez, and H. P. Martinez-Hernandez, "Development and Implementation of a Relay Switch Based on WiFi Technology," in *17th International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE)*, Mexico, 2020, pp. 1-6. doi: 10.1109/CCE50788.2020.9299142.

- [24] Hardware and Systems Engineering Design, "V-model in Electrical Systems Engineering," *hwe.design*, [Online]. Available: <https://tinyurl.com/maz33urd> [Accessed: May 18, 2025].

- [25] R. Morales-Caporal, R. E. Pérez-Loaiza, E. Bonilla-Huerta, J. Hernández-Pérez, and J. J. Rangel-Magdaleno, "IoT-Based LPG Level Sensor for Domestic Stationary Tanks with Data Sharing to a Filling Plant to Optimize Distribution Routes,"

Future Internet, vol. 16, no. 12, p. 479, Dec. 2024, doi: 10.3390/fi16120479.

[26] B5819W; *Datasheet*. Available online: <https://tinyurl.com/mrxax3xh2>. (accessed on 20 May 2025).

[27] EL357; *Datasheet*. Available online: <https://tinyurl.com/8tyh94kp>. (accessed on 20 May 2025).

[28] 74HC14D; *Datasheet*. Available online: <https://tinyurl.com/3skua6tp>. (accessed on 20 May 2025).

[29] PCF8574; *Datasheet*. Available online: <https://tinyurl.com/mtbsbhrv>. (accessed on 20 May 2025).

[30] P. Horowitz and W. Hill, *The Art of Electronics*, 3rd ed. Cambridge, U.K.: Cambridge University Press, 2015.

[31] LM358; *Datasheet*. Available online: <https://tinyurl.com/2x27f7yy> (accessed on 21 May 2025).

[32] MCP6002; *Datasheet*. Available online: <https://tinyurl.com/bj87hyze>. (accessed on 21 May 2025).

[33] A. Devasia, "Why is 4-20 mA Current Used for Industrial Analog Sensors?" *control.com*, 29 September 2022. [Online]. Available: <https://tinyurl.com/mtm3mpx2>. [Accessed: 21 May 2025].

[34] CH340C; *Datasheet*. Available online: <https://tinyurl.com/35x3pwvh>. (accessed on 22 May 2025).

[35] USBLIC6-2; *Datasheet*. Available online: <https://tinyurl.com/3zufwtpf>. (accessed on 22 May 2025).

[36] DS1307; *Datasheet*. Available online: <https://tinyurl.com/yhmzx2a6>. (accessed on 23 May 2025).

[37] G. Capwell, "Using Supercapacitors as RTC Power Backup," Abracan, Application Note, Jan. 2025. [Online]. Available: <https://tinyurl.com/78u9vcst>. [Accessed: 23 May 2025].

[38] R. Kalbitz and F. Puhane, "Supercapacitor – A Guide for the Design-In Process," *Würth Elektronik*, Application Note ANP077, Aug. 2020. [Online]. Available: <https://tinyurl.com/yb3kv73p>. [Accessed: 1 June 2025].

[39] ULN2803; *Datasheet*. Available online: <https://tinyurl.com/6m2h25yc>. (accessed on 23 May 2025).

[40] HF49FD/024-1H12; *Datasheet*. Available online: <https://tinyurl.com/5n7kbzzp>. (accessed on 24 May 2025).

[41] AO3400; *Datasheet*. Available online: <https://tinyurl.com/5n7enjp2>. (accessed on 24 May 2025).

[42] Toshiba Electronic Devices & Storage Corporation, "MOSFET Gate Drive Circuit," Application Note AKX00068, Jul. 2018. [Online]. Available: <https://tinyurl.com/25zyyb8a>. [Accessed: 25 May 2025].

[43] SS34; *Datasheet*. Available online: <https://tinyurl.com/mrx776x9>. (accessed on 24 May 2025).

[44] XL2596S-5.0E1; *Datasheet*. Available online: <https://tinyurl.com/3f3pwrz8>. (accessed on 24 May 2025).

[45] AMS1117-3.3; *Datasheet*. Available online: <https://tinyurl.com/3jb6wte6>. (accessed on 24 May 2025).

[46] B2412S-1W; *Datasheet*. Available online: <https://tinyurl.com/y7e9du74>. (accessed on 25 May 2025).

[47] IPC, IPC-2221B, *Generic Standard on Printed Board Design*. Bannockburn, IL, USA: IPC, November 2012.

[48] IPC, IPC-A-610G, *Acceptability of Electronic Assemblies*. Bannockburn, IL, USA: IPC, October 2017.

[49] M. Faheemuddin, "The Importance of PCB Line Spacing (Creepage & Clearance)," *ProtoExpress*, 22 March 2024. [Online]. Available: <https://tinyurl.com/4ccts955>. [Accessed: 28 May 2025].

[50] PLC IIoT ITA-1600, [Online]. Available: <https://github.com/gasca-cv/ITA-1600>

**Brayan Daniel Vazquez-Gasca** recibió el título de licenciatura en Ingeniería Electrónica con especialidad en automatización y control de la industria 4.0 por el Tecnológico Nacional de México / Instituto Tecnológico de Apizaco, Tlaxcala, México, en 2024. Actualmente cursa la maestría en Ingeniería Mecatrónica en la misma institución. Sus intereses de investigación incluyen el diseño e implementación de sistemas electrónicos embebidos, dispositivos IIoT e instrumentación industrial.

**Roberto Morales-Caporal**, received the B.E. degree in electromechanical engineering from the National Technological Institute of Mexico-Campus Apizaco (TecNM-ITA), Apizaco, México, in 1999, the M.Sc. degree in electrical engineering from the Graduate and Research Department, Higher School of Mechanical and Electrical Engineering (ESIME-Z), National Polytechnic Institute (IPN), México City, México, in 2001, and the Dr.-Ing. degree in electrical engineering from the University of Siegen, Siegen, Germany, in 2007. Since 2008, he has been a full-time Professor-Researcher at the Division of Graduate Studies and Research (TecNM-ITA). His research interests include discrete-time control systems, predictive control of power converters, predictive control of ac motor drives, hardware design, and the IoT. Prof. Morales-Caporal is a member of the National Research Fellows System Level 2 (SNII-2), Secretariat of Science, Humanities, Technology and Innovation (SECIHTI), México.

**Carlos Bueno-Avendaño** Doctor en Dispositivos Semiconductores. Graduado de la Benemérita Universidad Autónoma de Puebla. Profesor-Tecnológico Nacional de México, Instituto Tecnológico de Apizaco en el Departamento de Eléctrica-Electrónica (2019 a la fecha). Participando también en el área de posgrado en la Maestría en Ingeniería Mecatrónica y el Doctorado en Ciencias Profesor-Investigador BUAP Facultad de Ingeniería (2017-2020) SNI nivel 1 desde 2022 a la fecha. Área de trabajo: Mecatrónica, Ciencia de materiales, Nanociencia y nanotecnología, nano y micro-estructuras de ZnO y TiO<sub>2</sub>. Sensores de gas y foto sensores, celdas solares de óxidos metálicos.

**Rodolfo Eleazar Perez-Loaiza** has received his B.Sc. degree in Industrial Engineering and M.Sc. in Computer Science from Instituto Tecnológico de Apizaco (ITA), Apizaco, Tlaxcala, México, in 1999 and 2022, respectively, and the Ph. D. degree in Logistics and Supply Chain Management from Universidad Popular Autónoma del Estado de Puebla (UPAEP), in 2015. He is currently a full-time Professor of the division of graduate studies and research department, ITA. His area of interest is related to logistics network optimization, discrete simulation and management operations.

**Roy Maza-González** recibió el título de licenciado en Ingeniería Electrónica con especialidad en Control y Automatización en la Industria 4.0 por el Instituto Tecnológico de Apizaco, Tlaxcala, México en 2024. Actualmente cursa la maestría en Ingeniería Mecatrónica en la misma institución. Sus intereses de investigación incluyen el diseño electrónico, convertidores de potencia, sistemas de control digital y el aprovechamiento de energías renovables.

Fecha de recepción: 05 de junio de 2025, fecha de publicación en línea: octubre de 2025.

# Exploración Teórica de Arquitecturas de Microservicios en Entornos Contenerizados

**Samantha Yazmin Elizalde-Valencia<sup>1</sup>, José Juan Hernández-Mora<sup>2</sup>, María Guadalupe Medina-Barrera<sup>3</sup>, y Juan Ramos-Ramos<sup>4</sup>**

<sup>1</sup> Tecnológico Nacional de México – Instituto Tecnológico de Apizaco. San Andrés Ahuashuatepec, Municipio de Tzompantepec, Tlaxcala, C.P. 90491, México.

<sup>2</sup> Tecnológico Nacional de México – Instituto Tecnológico de Apizaco. San Andrés Ahuashuatepec, Municipio de Tzompantepec, Tlaxcala, C.P. 90491, México.

<sup>3</sup> Tecnológico Nacional de México – Instituto Tecnológico de Apizaco. San Andrés Ahuashuatepec, Municipio de Tzompantepec, Tlaxcala, C.P. 90491, México.

<sup>4</sup> Tecnológico Nacional de México – Instituto Tecnológico de Apizaco. San Andrés Ahuashuatepec, Municipio de Tzompantepec, Tlaxcala, C.P. 90491, México.

Autor de correspondencia: Autor. Samantha Yazmin Elizalde-Valencia (correo electrónico: [m23370041@apizaco.tecnm.mx](mailto:m23370041@apizaco.tecnm.mx)).

**Abstract-** This article analyzes container-based microservices architectures as a modern alternative to monolithic systems, highlighting their advantages in scalability, deployment flexibility, and fault isolation. Using a methodological approach that combines technology research engineering and agile practices, it examines how microservices address the key limitations of traditional architectures while introducing new operational complexities.

The findings reveal that microservices offer superior modularity and development speed, particularly for cloud applications. Containerization enables the independent deployment of services and the efficient use of resources, although it requires robust monitoring solutions for distributed environments. The study highlights how agile methodologies effectively manage and promote continuous collaboration with stakeholders.

The comparative analysis shows that microservices outperform monoliths in scenarios that demand high availability and rapid scaling. However, successful adoption requires careful consideration of organizational factors and technical challenges such as data consistency. The research provides insights for organizations transitioning to microservices.

**Keywords:** System Architecture, Microservices, Containerization, Scalability.

## I. INTRODUCCIÓN

En la creación de software, las arquitecturas monolíticas han predominado, estas son arquitecturas que incorporan todos los elementos, tales como interfaz de usuario, lógica empresarial y acceso a datos, en una sola unidad de despliegue [1]. Este modelo brinda beneficios iniciales, tales como sencillez en el desarrollo y despliegues conjuntos, lo que lo convierte en una buena opción para proyectos de tamaño reducido o equipos pequeños [2]. No obstante, conforme las aplicaciones se vuelven más complejas y los equipos se expanden, los sistemas monolíticos se topan con retos como problemas de mantenimiento, acoplamiento excesivo y un código complicado de administrar [3].

Las arquitecturas basadas en microservicios han surgido como una alternativa que posibilita dividir aplicaciones en servicios autónomos, cada uno con su propia lógica, mientras que la posibilidad de ejecutarse en contenedores asegura portabilidad y escalabilidad [4]. Este enfoque promueve la implementación constante, disminuye los peligros vinculados a modificaciones en el código y potencia la habilidad para ajustarse a nuevas demandas.

Por esta razón, compañías líderes como Netflix, Uber y Amazon, operan bajo estas estructuras. Netflix, vanguardista en la implementación de microservicios, emplea esta estructura para servir a más de 230 millones de usuarios alrededor del mundo. Al separar

características (como motores de sugerencias, transmisión de video y perfiles de usuario), Netflix consigue una elevada tolerancia a errores y un despliegue rápido de funciones. De forma parecida, el sistema de Uber basado en microservicios administra tareas en tiempo real, tales como la asignación de conductores, la geolocalización y el procesamiento de pagos, conservando respuestas con poca latencia. Amazon ilustra aún más este método, en el que servicios autónomos gestionan la administración de inventarios, pasarelas de pago y sugerencias a medida, facilitando el desarrollo simultáneo y la escalabilidad [5].

Este artículo analiza las bases, beneficios y retos de implementar una arquitectura de microservicios en contenedores. Además, se analizan casos de estudio y buenas prácticas vinculadas a la puesta en marcha de microservicios.

## II. PROBLEMATICA

Las arquitecturas monolíticas y los sistemas *legacy* (Sistemas obsoletos, críticos para operaciones empresariales, pero con alta dependencia de tecnologías desactualizadas y difícil mantenimiento) [6], presentan retos en entornos tecnológicos modernos, donde la agilidad y la escalabilidad son requisitos esenciales. A pesar de ser inicialmente eficaces, estos sistemas producen elevados gastos operativos debido a la falta de especialistas en tecnologías anticuadas y la complejidad de su mantenimiento, además de generar riesgos de seguridad al no poder poner en marcha actualizaciones esenciales [7]. Esta dificultad se intensifica cuando se compara con las necesidades actuales de integración con paradigmas como *cloud computing* e *IoT* (Internet of Things o Internet de las cosas en español). En este contexto, la arquitectura de microservicios, implementada por líderes tecnológicos como Netflix y Amazon, brinda beneficios clave al desacoplar funcionalidades en servicios ligeros, reutilizables y fácilmente escalables [8]. Precisamente por estas limitaciones de los sistemas tradicionales y las posibilidades que brindan los nuevos enfoques, se expone a continuación un estudio de las arquitecturas de microservicios, valorando su habilidad para abordar estos retos.

## III. ESTADO DEL ARTE

A pesar de que todavía existen sistemas que funcionan bajo esquemas anticuados y arquitecturas rígidas, cada vez más organizaciones están adoptando soluciones

basadas en microservicios y contenedores, evidenciando su efectividad en ambientes de producción. A continuación, se muestran ejemplos específicos que evidencian estas implementaciones exitosas.

En los casos analizados, los sistemas creados con estos métodos han demostrado avances notables en su capacidad de respuesta, mantenibilidad y eficiencia operativa, particularmente cuando se combinan con metodologías ágiles.

La investigación de Saransig [9] expone el desarrollo histórico de la arquitectura de software, centrándose en las arquitecturas monolíticas y de microservicios. La hipótesis principal plantea que, al implementarse en contenedores, la arquitectura de microservicios incrementa el rendimiento en un 15% en comparación con la arquitectura monolítica.

El estudio resalta que el análisis comparativo de rendimiento corrobora la hipótesis propuesta, evidenciando que las aplicaciones con arquitectura de microservicios en contenedores logran optimizar el uso de los recursos en comparación a las arquitecturas monolíticas. Estos hallazgos no solo satisfacen las metas concretas de la investigación, sino que también cuentan con el apoyo de investigaciones anteriores, incrementando la fiabilidad de los descubrimientos y posibilitando futuros estudios.

Aunque la obra se centra principalmente en la comparación de arquitecturas, también aborda las herramientas utilizadas para cada una de ellas y las estructuras en las que se están implementando. Este estudio ofrece una visión clara de cómo operan estas arquitecturas desde ese punto de vista, lo que aporta de manera significativa a la investigación en curso.

Por otro lado, Indrasiri [10], analiza la aplicación de microservicios en el desarrollo de aplicaciones, resaltando su habilidad para incrementar la escalabilidad y la rapidez frente a las arquitecturas monolíticas. Se utiliza una metodología basada en la generación e implementación de microservicios presentados como imágenes de contenedores, lo que simplifica su administración mediante herramientas como *Kubernetes* (Permite orquestar varios contenedores en distintos servidores como si fueran uno solo) [11]. Los hallazgos indican que esta arquitectura facilita una implementación ágil y una gestión más eficiente de la comunicación entre servicios, aspecto vital para aplicaciones complejas.

Además, la investigación de Auer [12] sugiere un enfoque de evaluación fundamentado en pruebas para la transición de sistemas monolíticos a microservicios, con el objetivo de reconocer indicadores esenciales como el rendimiento, la escalabilidad y los costos de

infraestructura. Los resultados indican que los microservicios en contenedores exhiben un desempeño superior (hasta un 15% superior en peticiones/segundo) en comparación con los monolíticos, aunque demandan un uso más intensivo de CPU debido a la sobrecarga de la red. La capacidad para escalar servicios de manera individual disminuye los gastos operativos, comprobando su efectividad en casos de prueba.

Respecto a la tesis de García [13], el propósito principal es desarrollar una aplicación que simplifique la adopción de animales de compañía, además de sensibilizar a la población acerca del mantenimiento y posesión de mascotas. Este problema necesita una respuesta que pueda expandirse en cuanto a usuarios y funciones. Para ello, se decide emplear un enfoque ágil que posibilita segmentar el proyecto en sprints o etapas breves. De igual manera, se propone como meta principal el diseño de API REST y contenedores virtuales.

La arquitectura elegida fusiona los fundamentos de la arquitectura hexagonal con la arquitectura de cebolla. Por lo tanto, se puede apreciar una base firme para construir un sistema que no solo es eficaz en cuanto a recursos, sino que también se puede ajustar con facilidad a modificaciones futuras.

En la tesis de Abad [14], examina el caso del Banco Central de Ecuador, que afrontaba desafíos importantes debido a su sistema monolítico convencional, tales como flexibilidad limitada y escalabilidad, fallos extendidos del sistema, problemas para incorporar nuevas tecnologías y cumplir con normativas, además de un desempeño restringido y un mantenimiento complicado. Para resolver estos problemas, la organización decidió cambiar a una arquitectura fundamentada en microservicios y microfrontends, que facilita un desarrollo modular y desacoplado, la reutilización de componentes en varios procesos y una escalabilidad autónoma por servicio. Los hallazgos de esta migración evidenciaron que los ambientes de desarrollo aislados son sumamente escalables y tienen la habilidad de ajustarse a demandas variables, garantizando así un desempeño óptimo y una escalabilidad eficaz. Además, los test de carga y estrés proporcionaron resultados confiables que corroboran la capacidad de la solución sugerida, corroborando que estas arquitecturas posibilitan a las organizaciones construir y administrar sistemas de software con mayor eficiencia, velocidad y capacidad de adaptación a las exigencias tecnológicas contemporáneas.

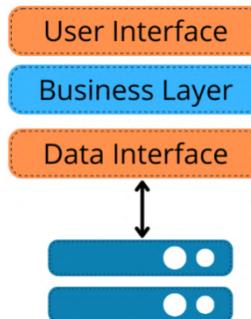

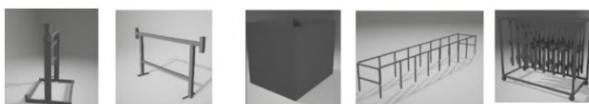

#### IV. ARQUITECTURA MONOLÍTICA

Para seguir con este estudio, es crucial mantener los conceptos básicos, iniciando con la arquitectura monolítica, que es un modelo de diseño de software en el que todos los elementos de una aplicación (interfaz de usuario, lógica de negocio y capa de acceso a datos) se integran en una única unidad de despliegue y comparten el mismo espacio de memoria y recursos [15]. Este enfoque se distingue por su fuerte interconexión y dependencia directa entre sus módulos, lo que complica la modificación individual de componentes, como se muestra en la Figura 1 [16]. La aplicación se establece como un único artefacto ejecutable, lo que facilita la distribución inicial pero restringe la actualización de funciones específicas.

Figura 1. Arquitectura Monolítica.

A pesar de que su sencillez permite su desarrollo en fases iniciales, los sistemas monolíticos se topan con retos críticos en términos de escalabilidad (al necesitar duplicar toda la aplicación para incrementar su capacidad) y mantenimiento (dado que las modificaciones impactan en el sistema en su totalidad).

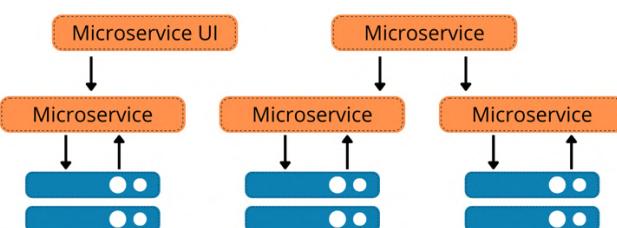

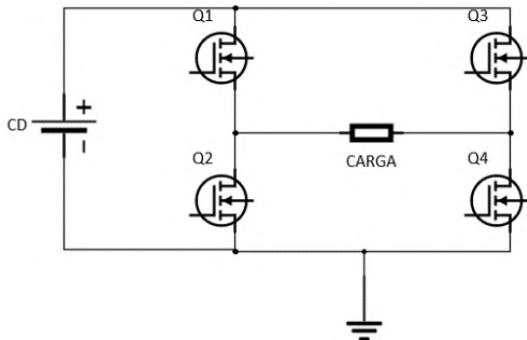

#### V. ARQUITECTURA DE MICROSERVICIOS

Los microservicios son una forma de arquitectura derivada de la Arquitectura Orientada a Servicios (SOA en inglés), que se distingue por la fragmentación de aplicaciones en servicios pequeños, autónomos y de alta especialización. Cada microservicio se centra en una única funcionalidad corporativa, se desarrolla de forma autónoma y se relaciona con otros servicios a través de interfaces claramente establecidas, usualmente a través de protocolos como REST (Figura 2) [16].

Figura 2. Arquitectura de Microservicios.

Una de las características fundamentales de los microservicios es que cada servicio puede ser creado, desplegado y escalado de manera autónoma, empleando distintas tecnologías y lenguajes de programación según se requiera. Esta estructura se diferencia de los sistemas monolíticos, en los que todas las funcionalidades se encuentran unidas en una única unidad de despliegue. Los microservicios brindan beneficios tales como una mayor resistencia, escalabilidad y sencillez para adoptar nuevas tecnologías. No obstante, también plantean retos, tales como la complejidad en la administración de la comunicación entre servicios, y la demanda de diversas habilidades técnicas en los equipos de desarrollo [17].

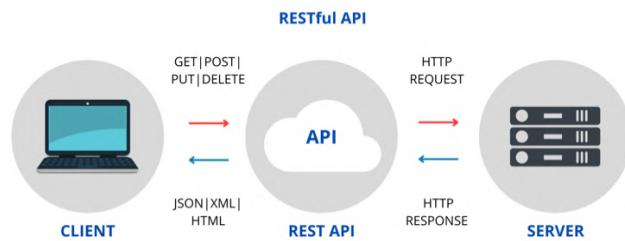

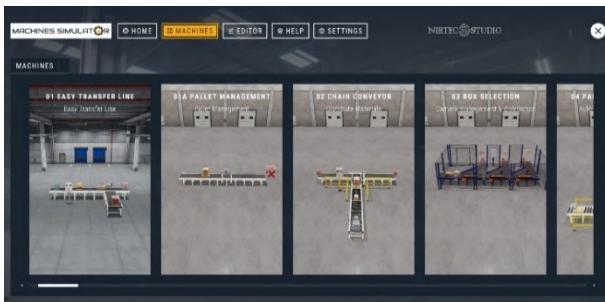

## VI. API REST

Una API RESTful (Representational State Transfer) es un enfoque arquitectónico para la creación de interfaces de programación de aplicaciones (APIs), como el protocolo HTTP, con el objetivo de facilitar la comunicación entre sistemas.

De acuerdo con Amazon Web Services [18], las APIs RESTful se basan en recursos identificables a través de URIs (Uniform Resource Identifiers), donde cada recurso puede ser gestionado a través de las operaciones estándar de consulta (GET), creación (POST), actualización (PUT) y eliminación (DELETE), en la que cada petición del cliente al servidor debe incluir toda la información requerida para su procesamiento, optimizando así la escalabilidad y el desempeño del sistema. Entre sus mayores beneficios sobresalen su simplicidad, escalabilidad y compatibilidad con diversos formatos de datos como JSON o XML, lo que las hace una elección predominante para la incorporación de servicios en aplicaciones web y móviles.

Figura 3. Funcionamiento API RESTful.

La Figura 3 [19], muestra una parte del funcionamiento esencial que realizan las APIs RESTful, resaltando los procedimientos fundamentales (GET, POST, PUT y DELETE), además de los formatos de intercambio convencionales como JSON, XML y HTML. La imagen describe el proceso de comunicación entre cliente y servidor, un cliente inicia la comunicación enviando una solicitud HTTP a la API REST, que procesa la petición y se comunica con el servidor; en consecuencia, el servidor responde con un HTTP.

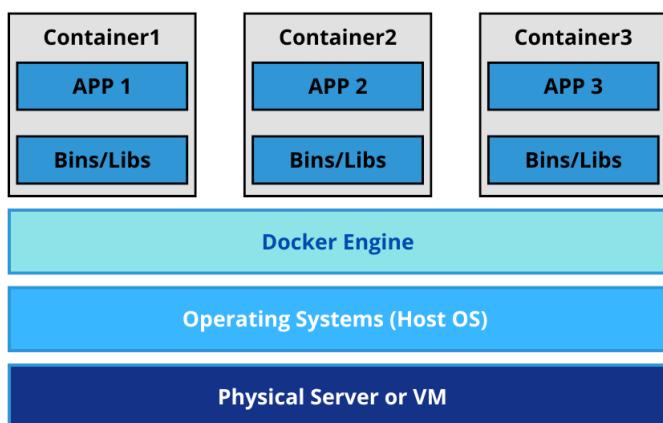

## VII. CONTENEDORES

Los contenedores han revolucionado la forma en que se desarrollan, implementan y ejecutan las aplicaciones en la actualidad. De acuerdo con Google Cloud [20], los contenedores son paquetes de software que contienen todo lo requerido para que una aplicación funcione de forma autónoma y eficiente: código, bibliotecas, herramientas y configuraciones, como se puede observar en la figura 4 [21]. Una de sus mayores fortalezas es la portabilidad, dado que pueden funcionar sin alteraciones en diferentes contextos (desarrollo local, producción o la nube), lo que permite una implementación consistente y disminuye los errores.

Además, su ligereza los convierte en perfectos para ambientes *cloud*, posibilitando la ejecución de múltiples aplicaciones en un solo servidor sin interrupciones, optimizando recursos y disminuyendo los gastos operativos.

Otro beneficio principal es su escalabilidad ágil y fácil. Los contenedores son una tecnología adaptable que revoluciona el desarrollo y la implementación de aplicaciones.

Figura 4. Estructura de contenedores de software.

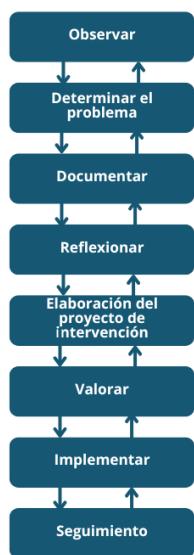

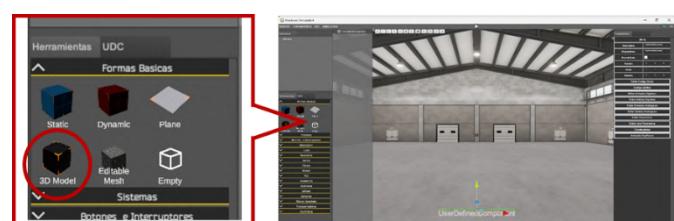

### VIII. METODOLOGÍAS

Para llevar a cabo el estudio de las arquitecturas de microservicios en contenedores, se empleará un enfoque de investigación tecnológica en ingeniería. Este método es apropiado para proyectos que no buscan formular nuevas teorías, sino reconstruir procesos a través de la adaptación y optimización de soluciones ya existentes. La investigación tecnológica facilitará el análisis de soluciones anteriores, la elección de sus componentes más destacados e incorporarlos a las demandas del proyecto [22].

Figura 5. Metodología de investigación propuesta.

La figura 5 muestra un proceso iterativo que inicia con la identificación de necesidades especiales y la definición exacta del problema, para luego pasar a una etapa de documentación de soluciones ya existentes. Despues, a través de un análisis crítico, se elabora un proyecto de intervención (como prototipos o

arquitecturas), que se evalúa en cuanto a factibilidad antes de su ejecución regulada. Luego, la observación de los resultados promueve modificaciones constantes, reiniciando el ciclo para mejorar la solución.

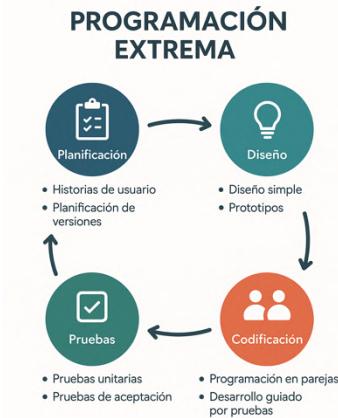

Mientras que en la etapa de intervención, se utilizarán técnicas ágiles, que mejoran la administración de proyectos de software a través de flexibilidad, constante cooperación con el cliente y entregas progresivas de productos funcionales. De acuerdo con Shafir [23], estas técnicas potencian la comunicación interna, incrementan la capacidad de adaptación a cambios y disminuyen los riesgos de fracaso. Elementos como el respaldo de la organización, la formación del equipo y la implicación directa del cliente son esenciales para su éxito. Asimismo, su método iterativo facilita la identificación de fallos en fases iniciales, optimizando recursos y gastos.

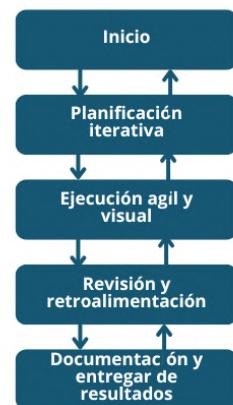

Figura 6. Metodología propuesta para desarrollo del proyecto de intervención.

Se inicia con la definición del problema, los objetivos del proyecto y la creación de un backlog con tareas priorizadas. Posteriormente, en la etapa de planificación se realizan iteraciones cortas (sprints) en las que el equipo selecciona las tareas más relevantes para desarrollarlas dentro de un flujo visual representado en un tablero Kanban, con columnas como "por hacer", "en proceso" y "terminado". A lo largo del proceso se llevan a cabo reuniones diarias breves para dar seguimiento, limitar el trabajo en curso y fomentar la colaboración. Al finalizar cada sprint se realiza una revisión de resultados y una retrospectiva para identificar áreas de mejora. Esta metodología permite adaptarse a los cambios, monitorear el avance en tiempo real y generar entregables funcionales durante todo el ciclo del proyecto.

Para fundamentar las bases de estas metodologías y la implementación de una arquitectura de microservicios, se trabajará en conjunto con el Instituto del Deporte de Tlaxcala (IDET). Las condiciones de su proyecto lo convierten en apropiado para probar este método, dado que necesita un sistema de alta durabilidad, facilidad para incorporar funciones y capacidad de escalado. La solución se organizará en microservicios autónomos, tales como el frontend, backend (que actuara como middleware), servicios de reportes y verificaciones de datos, entre otros. Este modelo facilitará la incorporación de nuevas funcionalidades a través de microservicios adicionales, sin alterar las operaciones actuales, asegurando de esta manera escalabilidad y modularidad.

## IX. TRABAJOS FUTUROS

Este artículo se centra en el estudio teórico de las arquitecturas de microservicios, tratando aspectos esenciales como las arquitecturas monolíticas y las arquitecturas fundamentadas en microservicios. Esta revisión proporciona un panorama que sirve como base para comprender las diferencias, ventajas y desafíos de cada enfoque, promoviendo de esta manera futuras investigaciones y avances en el área.

En trabajos posteriores se pretende profundizar en las metodologías utilizadas durante el proceso de investigación y en la elaboración del proyecto de intervención (Sistema de gestión medico deportiva del IDET), incluyendo la creación de una arquitectura que represente la interacción entre las diferentes capas del sistema. Además, se presentará una vista física que permita observar el funcionamiento real de una arquitectura de microservicios aplicada a un caso de prueba. También se detallarán aspectos técnicos como la configuración de APIs, contenedores y microservicios, lo cual permitirá comprender cómo se integran y comunican estos elementos dentro del sistema.

## X. CONCLUSIONES

El estudio realizado demuestra que las arquitecturas de microservicios constituyen un enfoque eficaz y escalable para el desarrollo de sistemas informáticos. En contraste a los sistemas monolíticos, que tienen limitaciones en términos de escalabilidad, mantenimiento y adaptabilidad, los microservicios brindan beneficios significativos, tales como modularidad, flexibilidad en la implementación y resistencia frente a errores, tal como lo respaldan varios estudios analizados.

Los microservicios no solo superan a los monolíticos en contextos que buscan alta disponibilidad y escalabilidad, tales como ambientes cloud o sistemas distribuidos, sino que también se adecuan a las demandas presentes de agilidad y eficacia en el desarrollo de software.

## REFERENCIAS

- [1] M. Fowler and J. Lewis, "Microservices: a definition of this new architectural term," *martinfowler.com*. Disponible: <https://martinfowler.com/microservices/>.

- [2] M. Fowler, "How to Break a Monolith into Microservices," *martinfowler.com*, 2019. Disponible: <https://martinfowler.com/articles/break-monolith-into-microservices.html>.

- [3] A. Guimarey, "Beneficios y riesgos de migrar una arquitectura monolítica a microservicios," *Universidad de Palermo*, 2020. Disponible: <https://www.researchgate.net/publication/348309479>.

- [4] AWS, "Monolítico frente a microservicios: diferencia entre arquitecturas de desarrollo de software," *Amazon Web Services*, s.f. Disponible: <https://aws.amazon.com/es/compare/the-difference-between-monolithic-and-microservices-architecture/>.

- [5] M. Sarzoza, "Arquitecturas de software que utilizan Netflix, Uber y más," *LinkedIn*, 2023. [En línea]. Disponible: <https://www.linkedin.com/pulse/arquitecturas-de-software-que-utilizan-netflix-uber-y-marcos-sarzoza-e6ytf/>

- [6] M. E. Barzola, "Migración semiautomática de sistemas Legacy hacia arquitecturas orientadas a servicios," Tesis de licenciatura, Lic. en Sistemas, Univ. Nac. de La Plata, 2018. Disponible: <https://sedici.unlp.edu.ar/handle/10915/82154>

- [7] D. Hossain y T. Sultana, "The role of Microservice Approach in Edge Computing: opportunities, challenges, and research directions," *ScienceDirect*, 2023. Disponible: <https://www.sciencedirect.com/topics/computer-science/monolithic-system>

- [8] LinkedIn, "Sistema Legacy: Qué es, características y migración con Whitecloud," dic. 26, 2024. Disponible: <https://www.linkedin.com/pulse/sistema-legacy-qu%C3%A9-es-caracter%C3%ADsticas-y-migraci%C3%B3n-B3n-con-whitecloud-s4tgc/>

- [9] A. F. Saransig Chiza, "Análisis de rendimiento entre una arquitectura monolítica y una arquitectura de microservicios - tecnología basada en contenedores," Tesis de Maestría, Escuela Politécnica Nacional, Ecuador, 2018. Disponible: <https://core.ac.uk/download/pdf/200323828.pdf>

- [10] K. Indrasiri, "Microservices in practice: Key architectural concepts of an MSA," WSO2, Tech. Rep., 2019. Disponible: <https://resources.wso2.com/whitepapers/microservices-in-practice-key-architectural-concepts-of-an-msa>

- [11] DZone, *Kubernetes in the Enterprise: A Guide to Orchestrating Containers at Scale*, DZone Refcardz, 2019. Disponible: <https://dzone.com/storage/attachments/14131598-dzone-kubernetesbundle.pdf>

- [12] F. Auer, "From monolithic systems to Microservices: An assessment framework," *Inf. Softw. Technol.*, 2021. Disponible: <https://www.sciencedirect.com/science/article/pii/S0950584921000793>

- [13] G. García Castañeda, "Diseño y desarrollo de una aplicación software, en el contexto del enfoque ágil, como soporte a la reducción del número de animales de compañía sin hogar en el

distrito metropolitano de Quito," Tesis de grado, Escuela Politécnica Nacional, Ecuador, 2024. Disponible: <https://bibdigital.epn.edu.ec/handle/15000/25528>

[14] F. L. Abad León and S. M. Guamán Cabrera, "Propuesta de una arquitectura basada en micro servicios y micro frontend con integración de una plataforma de mensajería y procesamiento de eventos masivos. Caso de estudio: Aplicación en sistemas de transferencia de fondos," *Universidad Politécnica Salesiana*, 2024. Disponible: <https://dspace.ups.edu.ec/bitstream/123456789/294071/UPS-CT011876.pdf>

[15] IBM, "Monolithic Architecture: Definition and Characteristics," 2023. Disponible: <https://www.ibm.com/think/topics/monolithic-architecture>.

[16] Medium, Monolithic vs. Microservices Architecture: Understanding the Key Differences, 2024. Disponible: <https://medium.com/@jain.yash1909/monolithic-vs-microservices-architecture-understanding-the-key-differences-7ddf328565d0>

[17] H. M. Ayas, R. Hebig, and P. Leitner, "An empirical investigation on the competences and roles of practitioners in Microservices-based Architectures," *The Journal of Systems & Software*, 2024. Disponible: [https://www.sciencedirect.com/science/article/pii/S0164121224001006?ref=pdf\\_download&fr=RR-2&rr=947fe8970b0c49df](https://www.sciencedirect.com/science/article/pii/S0164121224001006?ref=pdf_download&fr=RR-2&rr=947fe8970b0c49df)

[18] Amazon Web Services, "¿Qué es una API RESTful?," 2023. Disponible: <https://aws.amazon.com/es/what-is/restful-api/>

[19] onnuri.log, RESTful API. 2022. Disponible: <https://velog.io/@onnuri/RESTful-API>

[20] Google Cloud, "Contenedores en Compute Engine," 2024. Disponible: <https://cloud.google.com/compute/docs/containers?hl=es-419>

[21] Evolution. 2025. ¿Qué son los contenedores de software?. Disponible: <https://evolutioncode.us/que-son-los-contenedores-de-software>

[22] C. De la Cruz Casaño, *Metodología de la investigación tecnológica en ingeniería*. Universidad Continental, 2016. Disponible: [https://www.academia.edu/94930372/Metodología\\_de\\_la\\_investigación\\_tecnológica\\_en\\_ingeniería](https://www.academia.edu/94930372/Metodología_de_la_investigación_tecnológica_en_ingeniería)

[23] M. Shafir et al., "The Success Factors of Agile Methodologies in Software Development based on Developing Countries' Software Firms," *ScienceDirect*, 2025. Disponible: <https://www.sciencedirect.com/science/article/pii/S1877050925007069>

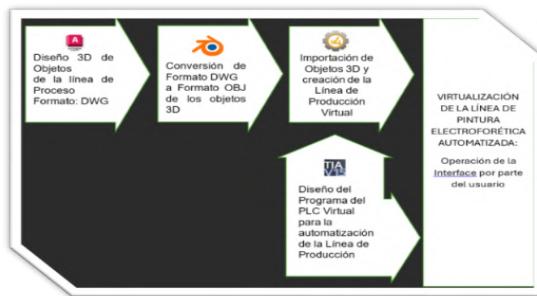

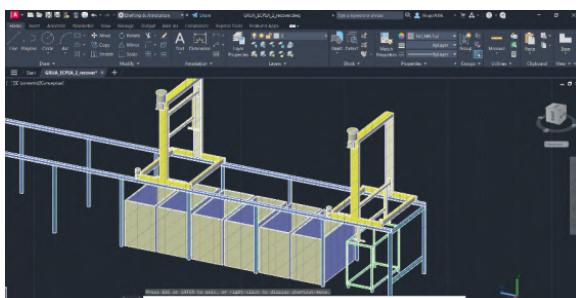

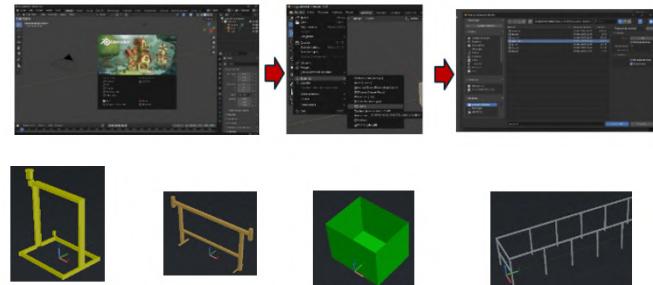

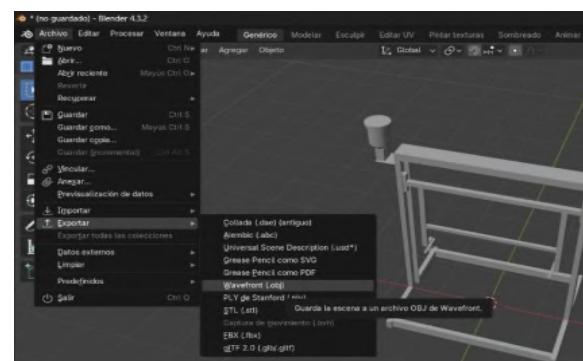

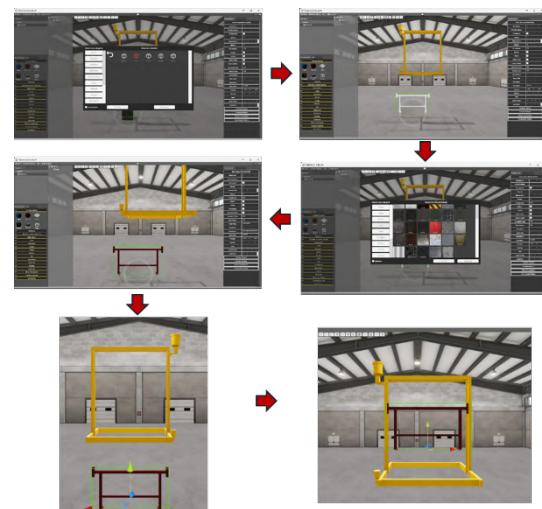

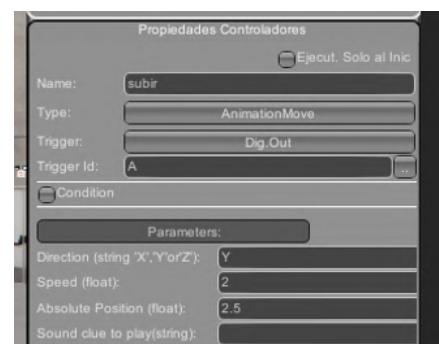

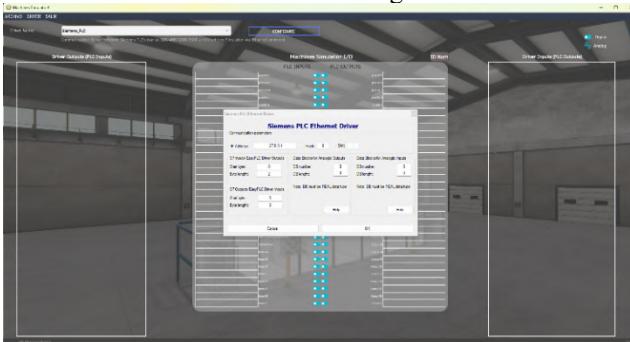

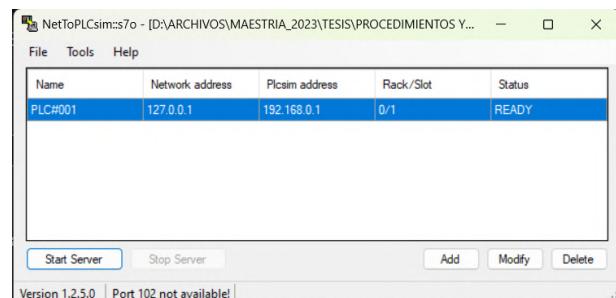

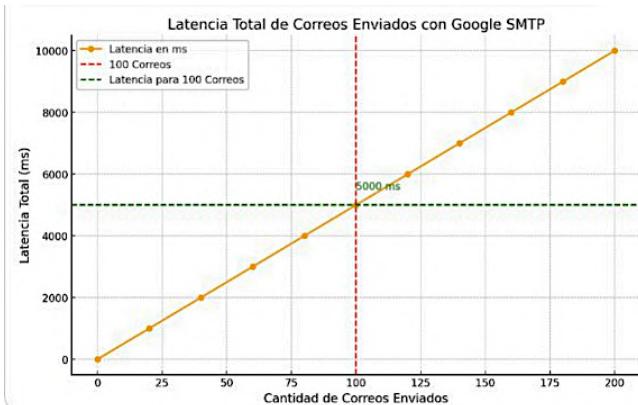

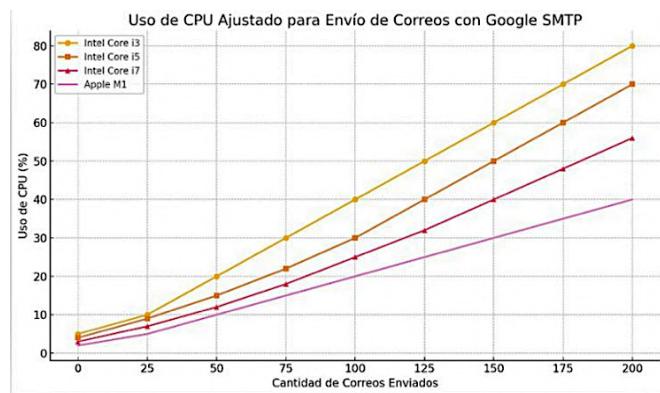

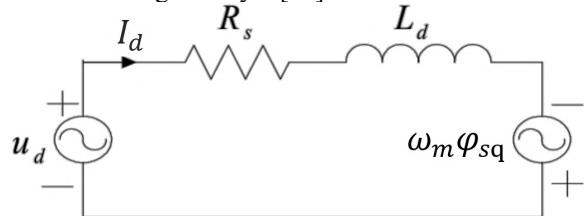

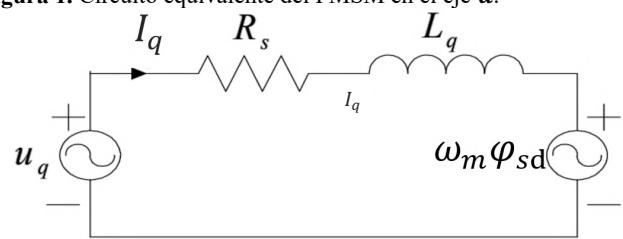

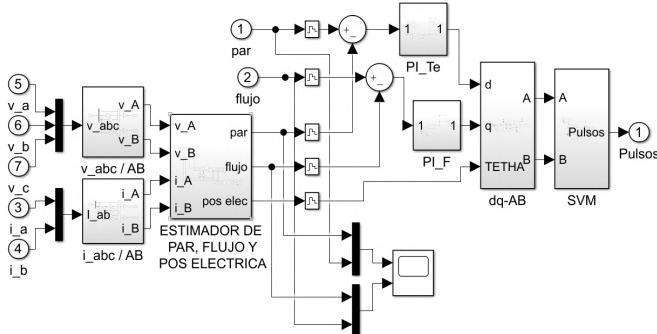

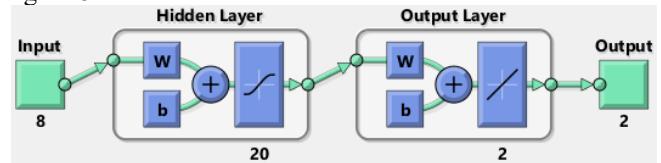

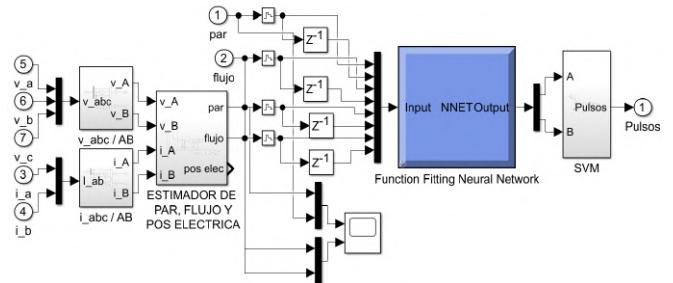

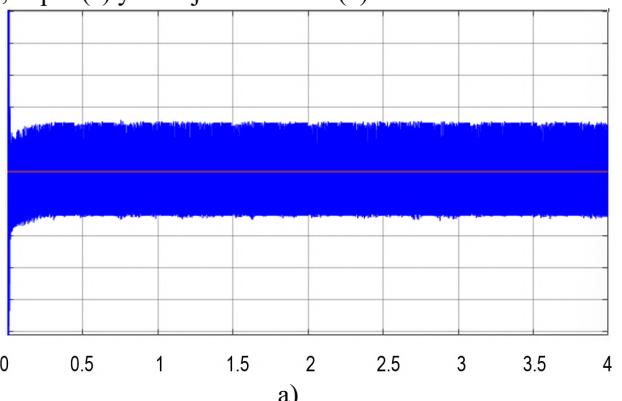

**SAMANTHA YAZMIN ELIZALDE VALENCIA** Ingeniera en Tecnologías de la Información y las Comunicaciones. Estudiante de Maestría en Sistemas Computacionales en el Instituto Tecnológico Nacional de México (TecNM) - Campus Apizaco.